# 386SX MAIN BOARD (25/33/40 MHz)

PT-319A

USER'S MANUAL

BEFORE INSTALLING THE PT-919A PLEASE READ THIS MANUAL COMPLETELY AND RETAIN IT FOR FUTURE REPERENCE

#### Note

- For the first time insulation with error recouge on the screen, please have the system on

the about 15-30 minutes no recharge the battery, their you can exten remem configuration.

- 2. Leave your system on for about 24 hours to recharge the bettery fully

- If you have switched off the computer system for more than two weeks, you might be required to repeat only 2 to nother the battery fails.

- To proved the Main Board, After the power is pwitched OFF, please wor'd records before you pull not the add-on-card.

#### Tradmark Acknowledgmouts

- BIM PC, PCXT and PC/AT all are registered trademarks of International Business Machines Corporation

- State is registered trademark of Iracl Corporation.

- AMD is registered traderests of Advanced Micro Devices Inc.

- AMI is registered trademark of American Megatrands Inc.

- Cycle is registered trademark of Cycle corporation.

- Sirc is regissered trademark of Silicon Architecture Technology Corp.

# TABLE OF CONTENTS

| SECTION 1:  | INTRODUCTION                         |       |

|-------------|--------------------------------------|-------|

| 1.1         | Overview                             | 3     |

| 1.2         | Check List                           | 3     |

| SECTION 2 : | SPECIFICATION                        |       |

| 2.1         | General Features                     | 4     |

| 2.2         | Jumpers and Connectors               | 4-6   |

| 2.3         | Memory Configurations                | 6     |

| 2.4         | Installation Procedures              | 7     |

| 2.5         | Installation of Co-processor         | 7     |

| SECTION 3:  | INPUT/OUTPUT CHANNEL SLOTS           |       |

| 3.1         | I/O Address Map                      | 8     |

| 3.2         | 62-Pin36-Pin I/O Bus                 | 9     |

| SECTION 4:  | HARDWARE COMPATIBILITY               |       |

| 4.1         | System Timers                        | 10    |

| 4.2         | System Interrupts                    | 10-11 |

| 4.3         | Direct Memory Access                 | 11-12 |

| 4.4         | Real Time Clock and Non-volatile RAM |       |

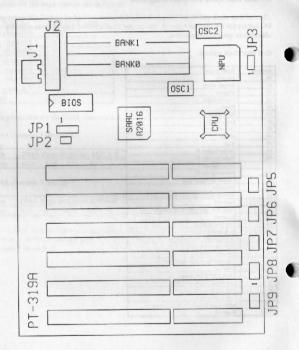

| SECTION 5:  | LAYOUT DIAGRAM                       |       |

| SECTION 6:  | BIOS SETUP                           |       |

| 6.1         | About CMOS Setup                     | 15    |

| 6.2         | Entering CMOS Setup                  | 15-16 |

| 6.3         | Getting Help                         |       |

| 6.4         | Using Setup                          |       |

| 6.5         | Standard CMOS Setup                  |       |

| 6.6         | Advanced CMOS Setup                  |       |

| 6.7         | Changing The Password                |       |

| 6.8         | Hard Disk Utility                    |       |

| 7.7         |                                      |       |

| 6.9         | Exiting Setup                        | 22    |

# SECTION 1

#### INTRODUCTION

#### 1.1 Overview

The RC2016A is a Single Chip AT high performance controller for the 25/33/40 MHz 3865X or Cx486SLC based PC-AT system. For 33/40 MHz operation, only 80/70ns DRAM is required and no cache memory is needed. Advanced independent I/O channel memory and on board memory refresh architecture assist better system performance. The memory management supports page and block interleave mode functions. Hardware EMS and flexible Shadow RAM features are also provided to implement a "SMALL WONDER" system.

Furthermore, the RC2016A Chip supports many advanced features such as STEPPING BUS, LOCAL DEVICE, USER ROM, SLOT POINTER, EMS, remapping of 384K memory, and PCMCIA applications that can let you achieve a very reliable and powerful system.

The RC2016A includes: dual 8237 DMA controller, dual 8259 interrupt controller, an 8254 programmable timer, a 74612 memory mapper, an 82288 bus controller, and an 82284 clock generator.

#### 1.2 Checklist

Please check your PT-319A package to ensure that it contains the following items:

- PT-319A Main board

- · PT-319A User's manual

If any of these items are missing or damaged, please contact your dealer or sales representative for assistance.

#### SPECIFICATIONS

#### 2.1 General Features

- IBM AT compatible

- Single Chip 386SX or Cx486SLC PC-AT Compatible Solution that supports 25/33/40 MHz non-cache system

- . Two banks, up to 16MB Memory on board using 256K, 512K, 1M or 4M type DRAM

- Page Mode and two-way Block Interleave DRAM access management

- Single (8-bit) SYSTEM BIOS ROM

- · Hardware EMS function

- · Programmable DRAM access timing

- . Independent DRAM refresh control for I/O CHANNEL and ON BOARD memory

- Programmable DRAM refresh rate and burst refresh mode

- Asynchronous I/O CHANNEL clock

- · Shadow RAM support, range from 0C0000 to 0FFFFF on 16K boundaries

- · Stepping address to reduce system noise

- · Control signals for 16MB user ROM on board and 16MB RAM on I/O channel

- Dedicated Alternative RESET to prevent losing CMOS RAM data

- Intelligent DRAM BANK identification and swapping

- 208-Pin QFP, 0.8u CMOS Technology

# 2.2 Jumpers and Connectors

| Jumpers / Connectors | Description                     |

|----------------------|---------------------------------|

| JP1                  | External Battery Connector      |

| JP2                  | Display Type Select Connector   |

| JP3                  | 387SX Clock Select              |

| JP5                  | Turbo Speed Connector           |

| JP6                  | RESET Connector                 |

| JP7                  | TURBO LED Connector             |

| JP8                  | Power LED and Keylock Connector |

| JP9                  | Speaker                         |

#### SECTION 2

#### SPECIFICATION

#### 2.2 Jumpers and Connectors

JP1 : External Battery Connector Pin Assignment

| 1 | +6V DC   |

|---|----------|

| 2 | Not Used |

| 3 | Ground   |

| 4 | Ground   |

JP2: Display Type Select Connector Pin Assignment

| Closed | Color      | <default></default> |

|--------|------------|---------------------|

| Open   | Monochrome |                     |

JP3 : 387SX Clock Select Pin Assignment

| 1-2 | Synchronous  | (CLK2) | <default></default> |

|-----|--------------|--------|---------------------|

| 2-3 | Asynchronous | (OSC2) | LC TO BE SOL        |

Note: If the speed of the CPU & Math Co-processor are in the same speed, then JP3 1-2 should be connected.

If the speed of the CPU & Math Co-processor aren't in the same speed, then JP3 2-3 should be connected. An additional oscillator needs to be added.

JP5: TURBO Speed Connector

| Closed | select high speed |

|--------|-------------------|

| Open   | select low speed  |

JP6 : Reset Connector Pin Assignment

| 1 | GND   |

|---|-------|

| 2 | Reset |

JP7: Turbo LED Connector Pin Assignment

|   | Anode (+)   |

|---|-------------|

| 2 | Cathode (-) |

#### JP8 Power LED and Keylock Connector

| 1 | LED Power        | Ī |

|---|------------------|---|

| 2 | NC               |   |

| 3 | Ground           |   |

| 4 | Keyboard Inhibit |   |

| 5 | Ground           |   |

#### **SECTION 2**

#### SPECIFICATION

#### 2.2 Jumpers and Connectors

# JP9 : Key Lock & Power LED Pin Assignment

| 1 | Data   |

|---|--------|

| 2 | NC     |

| 3 | Ground |

| 4 | +5V dc |

#### 2.3 Memory Configurations

| Total Memory | SIMM1 | SIMM2 | SIMM3 | SIMM4 |

|--------------|-------|-------|-------|-------|

| 512K         | 256K  | 256K  | None  | None  |

| 1M           | 256K  | 256K  | 256K  | 256K  |

| 1M           | 512K  | 512K  | None  | None  |

| 2M           | 512K  | 512K  | 512K  | 512K  |

| 2M           | 1M    | 1M    | None  | None  |

| 4M           | 1M    | 1M    | 1M    | 1M    |

| 8M           | 4M    | 4M    | None  | None  |

| 16M          | 4M    | 4M    | 4M    | 4M    |

#### 2.4 Installation Procedures

- 1. Connect power supply connectors

- 2. Plug in keyboard connector to the keyboard receptacle at the back

- 3. Install monochrome or color graphic display card in expansion slot

- 4. Select monochrome or color at JP2

- 5 Connector monitor cable to display board

- RC2016A-386SX has battery, however, you can plug in an external backup power back (+6Vdc) to external battery connector at the JP1

- 7. Plug in the 'Speaker' connector, 'Power LED' and 'Keylock' connector at the front

- 8. Turn on the monitor

- 9. Turn on the power supply

# SECTION 2

#### SPECIFICATION

#### 2.5 Installation of Co-processor

There is a 68 pin PLCC socket U9 for either Intel 80387 or Cyrix Cx387SLC Math coprocessor. Make sure OSC2 is corrected when math co-processor is added into the main board. PT-319A System Board can support math co-processor running either in Synchronous or Asynchronous Mode.

Refer to the section of Jumper Configurations for correct installation. Double check the settings before power up the system board.

If any question found, please contact your local dealer for assistance.

#### INPUT/OUTPUT CHANNEL SLOTS

# The input/output channel of PT-319A supports:

- Refresh of system memory from channel microprocessors

- Selection of data accesses (either 8-bit or 16-bit)

Interpret

- Interrupt

- DMA channels

- I/O wait-state generation

- Open-bus structure (allowing multiple microprocessors to share the system's resources including memory)

# 3.1 I/O address map

| Hex range    | Devices                                | Usage  |

|--------------|----------------------------------------|--------|

| 000-01F      | DMA controller I                       | System |

| 020-03F      | Interrupt controller 1                 | System |

| 040-05F      | Timer                                  | System |

| 060-06F      | 8042 (Keyboard)                        | System |

| 070-07F      | Real time clock,NMI mask               | System |

| 080-09F      | DAM page register                      | System |

| 0A0-0BF      | Interrupt controller 2                 | System |

| 0C0-0DF      | DMA controller 2                       | System |

| 0 <b>F</b> 0 | Clear math co-processor busy           | System |

| 0F1          | Reset math co-processor                | System |

| 0F8-0FF      | Math co-processor                      | System |

| 1F0-1F8      | Fixed disk                             | I/O    |

| 200-207      | Game I/O                               | I/O    |

| 278-27F      | Parallel printer port 2                | I/O    |

| 2F8-2FF      | Serial port 2                          | I/O    |

| 300-31F      | Prototype card                         | I/O    |

| 360-36F      | Reserved                               | I/O    |

| 378-37F      | Parallel printer port 1                | I/O    |

| 380-38F      | SDLC, bisynchronous 2                  | I/O    |

| 3A0-3AF      | Bisynchronous 1                        | 1/0    |

| 3B0-3BF      | Monochrome display and printer adapter | I/O    |

| 3C0-3CF      | Reserved                               | 1/0    |

| 3D0-3DF      | Color/graphic monitor adapter          | I/O    |

| 3F0-3F7      | Floppy diskette controller             | I/O    |

| 3F8-3FF      | Serial port 1                          | I/O    |

# SECTION 3

# INPUT/OUTPUT CHANNEL SLOTS

# 3.2 62-Pin, 36-Pin I/O Bus

|           |      | REAR | PANE    | EL  |             |

|-----------|------|------|---------|-----|-------------|

| GND       | BI   |      |         | Al  | -I/O CH CK  |

| RESET DRV | B2   |      | -       | A2  | SD7         |

| +5V DC    | B3   |      |         | A3  | SD6         |

| IRO9      | B4   | 1-   | -       | A4  | SD5         |

| -5V DC    | B5   |      | -       | A5  | SD4         |

| DRQ2      | B6   | 1-   | -       | A6  | SD3         |

| -12V DC   | B7   |      |         | A7  | SD2         |

| ows       | B8   |      |         | A8  | SD1         |

| +12V DC   | B9   |      |         | A9  | SD0         |

| GND       | B10  |      |         | A10 | -I/O CH RDY |

| -SMEMW    | B11  |      | 01/21/2 | AII | AEN         |

| -SMEMR    | B12  |      |         | A12 | SA19        |

| -IOW      | B13  |      |         | A13 | SA18        |

| -IOR      | B14  |      |         | A14 | SA17        |

| -DACK3    | B15  |      |         | A15 | SA16        |

| DRO3      | B16  |      |         | A16 | SA15        |

| -DACKI    | B17  | -    |         | A17 | SA14        |

| DRQ1      | B18  |      |         | A18 | SA13        |

| -REFRESH  | B19  | -    |         | A19 | SA12        |

| CLK       | B20  | 1.   |         | A20 | SAll        |

| IRO7      | B22  |      |         | A22 | SA9         |

| IRO5      | B24  |      |         | A24 | SA7         |

| IRQ3      | B25  |      |         | A25 | SA6         |

| -DACK2    | A26  |      |         | A26 | SA5         |

| T/C       | B27  | -    |         | A27 | SA4         |

| BALE      | B28  |      |         | A28 | SA3         |

| +5V DC    | B29  | -    |         | A29 | SA2         |

| OSC       | B30  | 1-   |         | A30 | SA1         |

| GND       | B31  |      |         | A31 | SA0         |

| -MEM CS16 | DI   | -    |         | CI  | SBHE        |

| -I/O CS16 | D2   |      | -       | C2  | LA23        |

| IRO10     | D3   | -    | 1000    | C3  | LA22        |

| IRQ11     | D4   |      |         | C4  | LA21        |

| IRQ12     | D5   |      |         | C5  | LA20        |

| IRQ15     | D6   | -    |         | C6  | LA19        |

| IRO14     | D7   | -    |         | C7  | LA18        |

| -DACK0    | D8   | -    |         | C8  | LA17        |

| DRQ0      | D9   |      | -       | C9  | -MEMR       |

| -DACK5    | D10  |      | -       | C10 | -MEMW       |

| DRQ5      | DII  |      |         | CII | SD08        |

| -DACK6    | D12  | -    |         | C12 | SD09        |

| DRQ6      | DI3  |      |         | C13 | SD10        |

| -DACK7    | D14  | -    |         | C14 | SD11        |

| DRQ7      | D15  | -    |         | C15 | SD12        |

| +5V DC    | D16  |      |         | C16 | SD13        |

| - MASTER  | D17  |      |         | C17 | SD14        |

| COUTD     | 7310 |      |         | C19 | 21315       |

#### HARDWARE COMPATIBILITY

#### 4.1 System Timers

The system has three programmable timer/counters controlled by an Intel 8254-2 timer/counter chip. These are channel 0 through 2, defined as follows:

| Channel 0 | System timer |      |  |

|-----------|--------------|------|--|

| GATE 0    | Tied on      |      |  |

| CLK IN 0  | 1.190Mhz OSC | mail |  |

| CLK OUT 0 | 8259A IRQ 0  |      |  |

| Channel 1 | Refresh Request Generator |  |  |

|-----------|---------------------------|--|--|

| GATE 1    | Tied on                   |  |  |

| CLK IN 1  | 1.190Mhz OSC              |  |  |

| CLK OUT I | Request Refresh Cycle     |  |  |

Note: Channel is programmed to generate a 15 microsecond period signal.

| Channel 2 | Tone Generation for speaker           |

|-----------|---------------------------------------|

| GATE 2    | Controlled by bit 0 of hex 61 PPI bit |

| CLK IN 2  | 1.190Mhz OSC                          |

| CLK OUT 2 | Used to drive the speaker             |

#### 4.2 System Interrupts

Sixteen levels of system interrupts are provided by the 80286 NMI & two 8259A interrupt controller chips. The following shows the various interrupt-level assignments in decreasing priority:

| Level                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | F                                            | unction                                                                                                                               |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|--|

| Microprocess                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                              | Parity or I/O channel check                                                                                                           |  |

| Interrupt con                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ctrollers                                    |                                                                                                                                       |  |

| CTLR 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | CILKZ                                        | Timer output 0                                                                                                                        |  |

| IRQ0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                              | Keyboard (Output buffer full)                                                                                                         |  |

| IRQ1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                              | Interrupt from CTLR 2                                                                                                                 |  |

| IRQ2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | RQ8                                          | Real time clock interrupt                                                                                                             |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | RO9                                          | Software redirected to INT 0AH(IRQ 2)                                                                                                 |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                              |                                                                                                                                       |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                              |                                                                                                                                       |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                              |                                                                                                                                       |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                              |                                                                                                                                       |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                              | Fixed disk controller                                                                                                                 |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                              | Reserved                                                                                                                              |  |

| and the second s |                                              | Serial Port 2                                                                                                                         |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                              | Serial Port 1                                                                                                                         |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                              | Parallel Port 2                                                                                                                       |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                              | Diskette controller                                                                                                                   |  |

| IRO7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                              | Parallel port 1                                                                                                                       |  |

| IRQ3 IRQ4 IRQ5 IRQ6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | RQ10<br>RQ11<br>RQ12<br>RQ13<br>RQ14<br>RQ15 | Reserved Reserved Numeric co-processor Fixed disk controller Reserved Serial Port 2 Serial Port 1 Parallel Port 2 Diskette controller |  |

# SECTION 4

# HARDWARE COMPATIBILITY

#### 4.3 Direct Memory Access

Each DMA channels are supported by the system. Two Intel 8237-5 DMA controller chips (Four channels in each chip) are used. DMA channels are assigned as follows:

| CTLR 1        | CTLR 2                  |

|---------------|-------------------------|

| Ch 0-Spare    | Ch 4-Cascade for CTLR 1 |

| Ch 1-SDLC     | Ch 5-Spare              |

| Ch 2-Diskette | Ch 6-Spare              |

| Ch 3-Spare    | Ch 7-Spare              |

Channels from 0 through 3 are contained in DMA controller 1. Transfers of 8-bit data, 8-bit I/O adapters and 8-bit or 16-bit system memory are supported by these channels. Each of these channels will transfer data in 64KB block throughout the 16-megabyte system address space.

Channels from 4 through 7 are contained in DMA controller 2. To cascade channels 0 through 3 to the microprocessor, use channel 4. Transfer of 16-bit data between 16-bit adapters and 16-bit system memory are then supported by channels 5, 6 & 7. DMA channels from 5 through 7 transfer data in 128K blocks throughout the 16-megabyte system address space. These channels will not transfer data on odd-byte boundaries.

The address for the page register are as follows:

| Page Register | I/O HEX address |  |  |

|---------------|-----------------|--|--|

| DMA channel 0 | 0087            |  |  |

| DMA channel 1 | 0083            |  |  |

| DMA channel 2 | 0081            |  |  |

| DMA channel 3 | 0082            |  |  |

| DMA channel 5 | 008B            |  |  |

| DMA channel 6 | 0089            |  |  |

| DMA channel 7 | 008A            |  |  |

| Refresh       | 008F            |  |  |

Address generation for the DMA channels is as follows:

For DMA channels 3 through 0

| Source  | DMA Page 1 | Registers 8237A-5 |

|---------|------------|-------------------|

| Address | A23A16     |                   |

For DMA channels 7 through 5:

| Source  | DMA Page Registers 8237A-5 |

|---------|----------------------------|

| Address | A23 A17 A16 A0             |

Note: The BHE and A0 addressing signals are forced to a logic 0. DMA channel addressees do not increase ordecrease through page boundaries (64KB for channels 0 through 3 and 128KB for channels 5 through 7).

# SECTION 4

#### HARDWARE COMPATIBILITY

#### 4.4 Real Time Clock and Non-volatile RAM

The real time clock and its 64 bytes of RAM information are backed up by 3.6V rechargeable DC battery (or 6V external battery). The internal clock circuitry uses 14 bytes while the rest is allocated to system configuration.

#### Real time clock address

| Address | Description                            |

|---------|----------------------------------------|

| 00      | Seconds                                |

| 01      | Second alarm                           |

| 02      | Minutes                                |

| 63      | Minute alarm                           |

| 04      | Hours                                  |

| 05      | Hour alarm                             |

| 06      | Day of week                            |

| 07      | Date of month                          |

| 08      | Month                                  |

| 09      | Year                                   |

| 0A      | Status register A                      |

| 0B      | Status register B                      |

| 0C      | Status register C                      |

| 0D      | Status register D                      |

| 0E      | Diagnostic Status byte                 |

| 0F      | Shutdown                               |

| 10      | Diskette drive type byte-drive A and B |

| 11      | Reserved                               |

| 12      | Fixed disk type byte-drive C and D     |

| 13      | Reserved                               |

| 14      | Low base memory                        |

| 16      | High base memory                       |

| 17      | Low expansion memory byte              |

| 18      | High expansion memory byte             |

| 19      | Extended fixed disk type-driver C      |

| IA      | Extended fixed disk type-driver D      |

| IB-2D   | Reserved                               |

| 2E-2F   | 2 byte CMOS checksum                   |

| 30      | Low expansion memory byte              |

| 31      | High expansion memory byte             |

| 32      | Data century byte                      |

| 33      | Information flags (set during power on |

| 34-3F   | Reserved                               |

# SECTION 5 LAYOUT DIAGRAM

## SECTION 6

#### BIOS Setup

#### 6.1 About CMOS Setup

Once the mainboard has been integrated into a system, you must run the mainboard's Setup program to record and/or change configuration information, such as the current date and time or your hard disk drive type. The Setup program is stored in read-only memory (ROM), and can only be accessed when you turn on or reset the system.

The settings you specify with the Setup program are recorded in a special area of memory called CMOS RAM. This memory is backed up by a battery so that it will not be crused when you turn off or reset the system. Whenever you turn on the power, the system reads the settings stored in CMOS RAM and compares them to the equipment check conducted during the POST. If an error occurs, an error message will be displayed on screen, and you will be prompted to run the Setup program.

The BIOS Setup program is accessed through a menu which allows you to easily configure your system. Standard CMOS Setup allows you to record basic system information regarding date and time, video type and installed drives. Advanced CMOS Setup gives you access to the advanced features supported by the BIOS and your mainboard's RC2016A-386SX chipset.

#### 6.2 Entering CMOS Setup

After powering on the system and in the course of the system POST, you will be presented with the screen depicted below.

- To enter the Setup program at this time, press the [Del] key. This will display the first page

of the AMI BIOS Setup menu, which is illustrated on the next page.

- If you do not press these keys at the correct time and the system boots, press [Ctrl-Alt-Del] to restart the system and try again.

- If you do not press the key at the correct time and the system fails to boot, an error message will be displayed (such as KEYBOARD ERROR) and you will again be asked to

#### RUN SETUP UTILITY

#### Press <F1> to resume

This is normal. Press [Ctrl-Alt-Del] at this time to restart the system and then enter Setup by pressing the [Del] key.

#### SECTION 6

# BIOS SETUP

#### 6.2 Entering CMOS Setup

- After you enter Setup, you will be presented with the main menu of the AMI Setup program, which is pictured below.

- Select Standard CMOS Setup to access the Standard CMOS Setup menu, which is discussed in section 6.4 below.

- Select Advanced CMOS Setup to access the Advanced CMOS Setup menu, which is discussed in section 6.5 below.

#### The Advanced Chipset Setup menu option is not implemented.

- Select Auto Configuration with BIOS Defaults to load the default system values. You will be prompted for confirmation, and notified that the values have been loaded.

- Select Auto Configuration with Power-On Defaults to load the default power-on values, which disable all performance options. This option serves a useful diagnostic function in the event of a compatibility problem. You will be prompted for confirmation, and notified that the values have been loaded.

- Select Change Password to access the password security menu, which is discussed in section 6.6 below.

- Select Hard Disk Utility to access the hard disk utility menu, which is discussed in section 6.7 below.

- Select Write to CMOS and Exit to save your configuration and exit the Setup program.

You will be prompted for confirmation before the changes are written to CMOS and the system reboots.

- Select Do Not Write to CMOS and Exit to cancel any changes to your configuration and exit the Setup program You will be prompted for confirmation before the system reboots.

#### 6.3 Getting Help

- Help screens are displayed for each option in the Standard CMOS Setup menu, and can be

accessed in the Advanced CMOS. Setup menu by pressing [F1]. A"pop-up" window will

appear, similar to the one pictured below, listing the available selections for that option. To

exitthe Help window, press any key.

- If you have trouble reading the Setup menu, toggle the menu colors by pressing [F2] for background color and [F3] for foreground color.

#### SECTION 6

#### BIOS SETUP

#### 6.4 Using Setup

The following keys and key combinations are used to maneuver among Setup options and to change values.

To move the highlight bar from one option to another, use cursor (or arrow) keys, with [NumLock] turned off.

- · Press [PgUp] or [PgDn] to change the value of option.

- Press the [Esc] key to exit back to the AMI Setup program's main menu.

- · Press [F5] to restore the values that were resident when the Setup program was entered.

# 6.5 Standard CMOS Setup

The Standard CMOS Setup menu allows you to specify the following system configuration information:

Date and time. Enter the date and time, respectively.

Daylight saving. Choose Enabled or Disable.

Hard disk C. and D. type. The BIOS supports 47 fixed disk drive types, 46 of which are predefined in the ROM-resident table. If your hard disk type is not directly supported, you may need to manually enter the correct parameters (heads, cylinders, sectors, write precompensation, and landing zone) under type 47. If no hard drive is installed, select Not Installed.

- Floppy drive A: and B: Enter the diskette configuration your system is equipped with. If

no floppy drive is installed, select Not Installed.

- Primary display. Enter the type of video display adapter you have connected to your system.

The AMI BIOS will usually auto detect the correct type.

- · Keyboard. Choose Installed or Not Installed (e.g. for a file server), as appropriate.

#### SECTION 6

#### BIOS SETUP

#### 6.6 Advanced CMOS Setup

The Advanced CMOS Setup menu allows you to set various BIOS and chipset performance options, as illustrated and described below.

|                                                                                                                                                                                                 |                                                                                   | - ADVANCED CMOS SETUP<br>Is Inc., All Rights Reserve                              | ed                                                                            |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|-------------------------------------------------------------------------------|

| Numeric Processor Test<br>Floppy Drive Seek At Boot<br>System Boot Up Sequence<br>Fast Gate A20 Option<br>Password Checking Option<br>Video ROM Shadow C000,32K:<br>System ROM Shadow F000,64K: | 500 15 Disabled Enabled Enabled Enabled 0:300 Enabled On Disabled Disabled C:, A: | ATBUS Stepping<br>Refresh ( rate burst)<br>Ras Precharge time<br>Ras to Cas Width | : Disabled<br>: Enabled<br>: 8 burst<br>: 8 burst<br>: CLK2 * 4<br>: CLK2 * 4 |

Sel (Ctrl)Pu/Pd:Modify F1:Help F2/F3:Color F5:Old Values F6:BIOS Setup Defaults F7:Power-On Defaults

- Typematic Rate Programming. This option enables or disables programming of the keystroke repeat rate, which is adjusted by means of the next two options.

- Typematic Rate Delay (msecs). If Typematic Rate Programming is enabled, this option allows you to specify the delay between holding down a key and when the character begins repeating.

- Typematic Rate (Char/Sec). If Typematic Rate Programming is enabled, this option allows

you to specify the rate at which a character keeps repeating.

- Above 1MB Memory Test. When Enable this option causes memory above 1MB to be checked during the POST. If Disable, only the first 1MB is checked during the POST.

- Memory Test Tick Sound. This option enables or disables an audible sound during the POST memory test.

- Memory Parity Error Check. This option enables or disables BIOS memory parity error checking routines.

- Hit <DEL> Message Display. Disable this option to prevent the "Hit <DEL>, If you want to run Setup" message from appearing on screen after the POST.

#### SECTION 6

#### BIOS SETUP

## 6.6 Advanced CMOS Setup

- Hard Disk Type 47 RAM Area. Select 0:300 unless your system is running a network operation system which uses the 0:300 address for system operations.

- Wait for <F1> If Any Error. Disable this option to eliminated the need for any user response

to a non-fatal error condition during the POST.

- System Boot Up Num Lock. Select On or Off to enable or disable the keyboard NumLock switch.

- · Numeric Processor. Select Installed if you have installed an 80387SX numeric co-processor.

- Floppy Drive Seek at Boot. Select Disabled to speed up the boot process and prevent possible damage to the diskette drive heads.

- System Boot Up Sequence. As a general guideline, select A then C (A:, C:) if you will

normally boot the operating system from a floppy disk. Select C then A (C:, A:) if you will

normally boot the operating system from the hard disk drive.

- · Gate A20 Emulation. Gate-A20 is controlled by Chipset.

- Password Checking Option. This allows you to optionally limit access to the system or to

the Setup program alone. If you enable security by selecting Always or Setup, access to the

system and/or the Setup program is restricted to valid password entry.

- Video ROM Shadow. This option allows you to shadow the video BIOS address range from C000h to C7FFH. Shadow RAM is a technique that copies slower 8-bit or 16-bit ROMs to faster RAM system memory. Unless you encounter a compatibility problem, you should enable video ROM shadowing to improve performance.

- System ROM Shadow. This option allows you to shadow the system BIOS address range from F000h to FFFFh. Shadow RAM is a technique that copies slower 8-bit or 16-bit ROMs to faster RAM system memory. Unless you encounter a compatibility problem, you should enable system ROM shadowing to improve performance.

#### BIOS SETUP

#### 6.6 Advanced CMOS Setup

Memory Wait State. This option allows you to enable or disable a DRAM access wait-state.

Unless you encounter a compatibility problem, you should set this option to Disabled for improved performance.

#### 6.7 Changing the Password

If the Password Checking Option under the Advanced CMOS Setup menu is set to either Always or Setup, password entry is required every time the system boots or an attempt is made to enter the Setup program, respectively. The Change Password menu allows you to change the current password, as illustrated below.

- To change the current password, select the Change Password menu option from the Setup

main menu. You will be prompted to enter the old password before gaining access. If this

is the first time you attempt to change passwords, the default password is AMI.

- After entering the correct current password, you will be prompted to enter a new password.

The password can be no longer than 6 characters. After entering the new password, you will be prompted to enter it a second time for confirmation. If the second entry matches the first, you will be notified that the new password has been installed.

If you forget or lose your password, the only way to access the system and/or Setup program is to discharge the CMOS battery. When the CMOS battery becomes corrupted or is discharged, the default password becomes AMI.

#### BIOS SETUP

#### 6.8 Hard Disk Utility

If the Hard Disk Utility menu is selected from the Setup main menu, you will be presented with three options: Hard Disk Format, Auto Interleave, and Media Analysis. Performing any of these operations will destroy all data on the hard disk, so be sure to backup your data before selecting any of these options.

- Hard Disk Format. This option performs a low-level format if the hard disk. Note that many hard drives are factory low-level formatted, and should not be re-formatted. Check with your hard disk manufacturer before selecting this option.

- Auto Interleave. This option determines the optimum inter-leave factor prior to a low-level format of the hard disk.

- Media Analysis. This option analyzes each track on the hard disk to determine if it is usable.

If it is unusable, the track is marked as "bad" so that the system will not write data to it.

Many manufacturers provide a list of bad tracks so that this step may not be necessary.

IDE and SCSI hard drive should not normally be low-level formatted. Refer to your hard disk dealer or manufacturer before using the AMI Hard Disk Utility.

#### 6.9 Exiting Setup

- . To exit Sctup, press [Esc] to return to the Setup main menu.