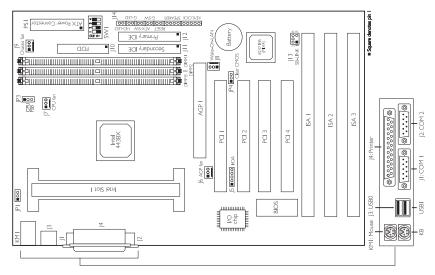

## P2XBL

## **DIP Switch Settings of the Processors**

| Processor |                     | Frequency | CLACI                                              | Processor           |                     | Frequency |                                                    | O Black rectangle denotes the part                                   |

|-----------|---------------------|-----------|----------------------------------------------------|---------------------|---------------------|-----------|----------------------------------------------------|----------------------------------------------------------------------|

| 66MHz     | 100MHz              | Ratio     | SWI                                                | 66MHz               | 100MHz              | Ratio '   | SWI                                                | that is protruding the "adjustable"  SWI 1234  In the example above: |

| 233MHz    | 350MHz              | 3.5×      | O   2 3 4                                          | 400MHz              | Future<br>processor | 6x        | O   2 3 4                                          |                                                                      |

| 266MHz    | 400MHz              | 4x        | 0 1 2 3 4<br>1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 | 433MHz              | Future<br>processor | 6.5×      | 0 1 2 3 4<br>↑                                     |                                                                      |

| 300MHz    | 450MHz              | 4.5x      | 0 1 2 3 4<br>N 1 2 3 4                             | Future<br>processor | Future<br>processor | 7x        | 0 1 2 3 4<br>1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 | Switch 1: Off<br>Switch 2: Off<br>Switch 3: On                       |

| 333MHz    | 500MHz              | 5×        | 0 1 2 3 4<br>1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 | Future<br>processor | Future<br>processor | 7.5×      | 0 1 2 3 4<br>1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 | Switch 4: On                                                         |

| 366MHz    | Future<br>processor | 5.5×      | 0   2 3 4                                          | Future<br>processor | Future<br>processor | 8×        | 0 1 2 3 4<br>1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 |                                                                      |

Note: The voltage regulator will automatically be set according to the voltage of the processor.

**JPI (Wake-On-Keyboard/Mouse) -** 2-3 On: Enable; 1-2 On: Disable (default)

By default, JPI is disabled. Make sure "Keyboard/Mouse Power On" in the Integrated Peripherals setup of the Award BIOS is also disabled. If JPI was previously enabled with a password set in the "KB Power On Password" field, and now you wish to disable the Wake-On-Keyboard (password) function, make sure to set the "Keyboard/Mouse Power On" field to Disabled prior to setting JPI to disabled. You will not be able to boot up the system if you fail to do so.

JP3 (CPU's FSB Select) - I-2 On: Auto (default); 2-3 On: 66MHz; I-2-3 Off: I00MHz

JP4 (Clear CMOS Data) - 1-2 On: Normal (default); 2-3 On: Clear CMOS Data Before clearing the CMOS data, make sure to power-off your system and unplug the power cord.