# Chapter 2

# **Hardware Installation**

This chapter gives you a step-by-step procedure on how to install your system. Follow each section accordingly.

**Caution:** Electrostatic discharge (ESD) can damage your processor, disk drives, expansion boards, and other components. Always observe the following precautions before you install a system component.

- Do not remove a component from its protective packaging until you are ready to install it.

- 2. Wear a wrist ground strap and attach it to a metal part of the system unit before handling a component. If a wrist strap is not available, maintain contact with the system unit throughout any procedure requiring ESD protection.

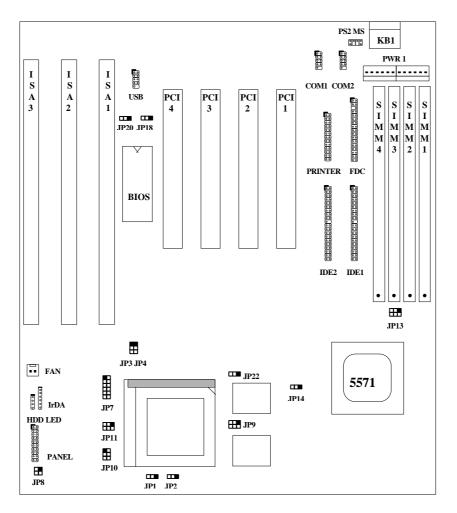

# 2.1 Jumper and Connector Locations

The following figure shows the locations of the jumpers and connectors on the system board:

#### Jumpers:

| JP1,JP2:       | CPU frequency ratio                                      |

|----------------|----------------------------------------------------------|

| JP3,JP4,JP13:  | CPU external (bus) clock                                 |

| JP7:           | CPU core voltage setting ∜core)                          |

| JP8:           | I/O voltage setting [∕io)                                |

| JP9,JP10,JP11: | CPU type (Single/Dual voltage)/cpuio source selection.)  |

| JP22:          | CPU Burst Mode (Linear for Cyrix, Toggle for Intel/AMD.) |

| JP14:          | Clear CMOS                                               |

| JP18:          | Onboard Super I/O enable/disable                         |

| JP20:          | Onboard PS/2 mouse enable/disable                        |

#### Connectors:

| KB1:     | AT keyboard connector                 |

|----------|---------------------------------------|

| PWR1:    | AT (PS/2) power connector             |

| PS2 MS:  | PS/2 mouse connector                  |

| USB:     | USB connector                         |

| COM1:    | COM1 connector                        |

| COM2:    | COM2 connector                        |

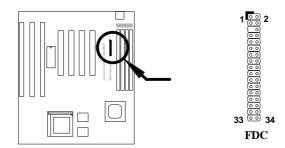

| FDC:     | Floppy drive connector                |

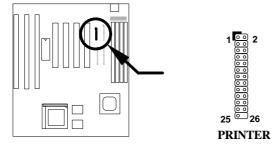

| PRINTER: | Printer connector                     |

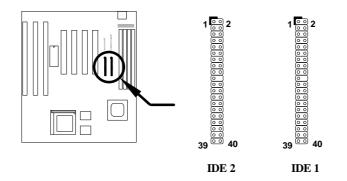

| IDE1:    | IDE1 primary channel                  |

| IDE2:    | IDE2 secondary channel                |

| FAN:     | CPU fan connector                     |

| IrDA:    | IrDA (Infrared) connector             |

| HDD LED: | HDD LED connector                     |

| PANEL:   | Front panel (Multifunction) connector |

#### 2.2 Jumpers

Jumpers are made by pin headers and plastic connecting caps for the purpose of customizing your hardware. Doing so requires basic knowledge of computer hardware, be sure you understand the meaning of the jumpers before you change any setting. The onboard jumpers are normally set to their default with optimized settings.

On the mainboard, normally there is a bold line marked beside pin 1 of the jumper, sometimes, there are numbers also. If we connect (short) plastic cap to pin 1 and 2, we will say set it at 1-2, and when we say jumper is open, that means no plastic cap connected to jumper pins.

2

Open

Short

Jumper set at 1-Jumper set at 2-3

2-4

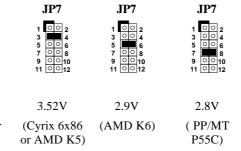

### 2.2.1 Setting the CPU Voltage

| <u>JP7</u> | CPU Core Voltage (Vcore) |

|------------|--------------------------|

| 1-2        | 3.45V (default for P54C) |

| 3-4        | 3.52V (Cyrix or AMD)     |

| 5-6        | 2.9V (AMD K6)            |

| 7-8        | 2.8V (PP/MT P55C)        |

| 9-10       | 2.7V                     |

| 11-12      | 2.5V                     |

|            |                          |

JP7 is used to select CPU core voltage (Vcore), normally it is set to default 3.45V for INTEL Pentium P54C. It must be changed if you have CPU with different core voltage, such as INTEL PP/MT (P55C), AMD K5/K6 and Cyrix 6x86, refer to the CPU specification for more details.

JP7

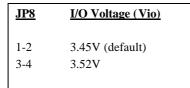

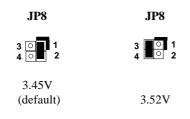

**JP8** is reserved for test only, which sets the voltage of onboard chipset and PBSRAM (Vio). When you are using dual voltage CPU, JP8 also provides CPU I/O voltage (Vcpuio).The default is 3.45V.

| JP9<br>Close<br>Open | JP10<br>Open<br>Close | JP11<br>Close<br>Open | CPU Type (Vcpuio)<br>Single voltage CPU<br>Vcpuio = Vcore<br>(default)<br>Dual voltage CPU<br>Vcpuio = Vio<br>(PP/MT P55C) | Set the jumper <b>JP9</b> , <b>JP10</b> and <b>JP11</b> according to the type of CPU. They are actually the selection of CPU I/O Voltage (Vcpuio). Normally, for single voltage CPU, Vcpuio is equal to Vcore, but for CPU that needs dual voltage such as PP/MT |

|----------------------|-----------------------|-----------------------|----------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                      |                       |                       | (PP/MT P55C)                                                                                                               |                                                                                                                                                                                                                                                                  |

(Vcpuio = Vcore)

(Vcpuio = Vio)

| CPU Type         | Vcore | Vio   | Vcpuio | JP7 | JP8 | JP9    | JP10   | JP11   |

|------------------|-------|-------|--------|-----|-----|--------|--------|--------|

| INTEL P54C       | 3.45V | 3.45V | Vcore  | 1-2 | 1-2 | Closed | Open   | Closed |

| INTEL PP/MT      | 2.8V  | 3.45V | Vio    | 7-8 | 1-2 | Open   | Closed | Open   |

| AMD K5           | 3.52V | 3.45V | Vcore  | 3-4 | 1-2 | Closed | Open   | Closed |

| (Single voltage) |       |       |        |     |     |        |        |        |

| AMD K6           | 2.9V  | 3.45V | Vio    | 5-6 | 1-2 | Open   | Closed | Open   |

| Cyrix 6x86       | 3.52V | 3.45V | Vcore  | 3-4 | 1-2 | Closed | Open   | Closed |

| Cyrix 6x86L      | 2.8V  | 3.45V | Vio    | 7-8 | 1-2 | Open   | Closed | Open   |

Caution: Above table is possible settings of current CPU available on the market. The correct setting may vary because of new CPU product, refer to your CPU specification for more details.

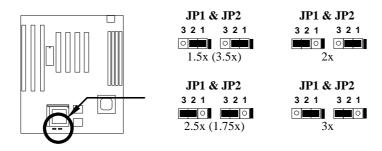

#### 2.2.2 Selecting the CPU Frequency

| <u>JP1</u> | <u>JP2</u> | CPU Frequency Ratio |

|------------|------------|---------------------|

| 1-2        | 1-2        | 1.5x (3.5x)         |

| 2-3        | 1-2        | 2x                  |

| 2-3        | 1-2        | 2x                  |

| 2-3        | 2-3        | 2.5x (1.75x)        |

| 1-2        | 2-3        | 3x                  |

Intel Pentium, Cyrix 6x86 and AMD K5/K6 CPU are designed to have different Internal (Core) and External (Bus) frequency. The ratio of Core/Bus frequency is selected by **JP1** and **JP2**, which CPU is using to multiply external clock and produce internal frequency.

Core frequency = Ratio \* External bus clock

**Note:** The feature CPU Intel PP/MT 233MHz is using 1.5x jumper setting for 3.5x frequency ratio, and AMD PR166 is using 2.5x setting for 1.75x frequency ratio.

**Note:** The future CPUs have not been tested by AOpen Quality Test Department. It is possible that this mainboard can not support these future CPUs.

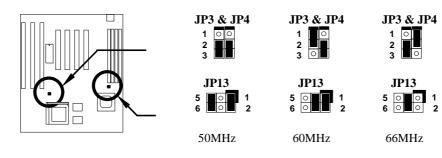

| JP3 | JP4 | <u>JP13</u> | CPU External |

|-----|-----|-------------|--------------|

|     |     |             | <u>Clock</u> |

| 2-3 | 2-3 | 1-2 5-6     | 50MHz        |

| 1-2 | 2-3 | 1-2 3-4     | 60MHz        |

| 2-3 | 1-2 | 3-4         | 66MHz        |

|     |     |             |              |

**JP3, JP4** and **JP13** are the selections of CPU external clock (bus clock), which is actually the clock from clock generator.

**Caution:** Following table are possible settings of current CPU available on the market. The correct setting may vary because of new CPU product, refer to your CPU specification for more details.

| Intel<br>Pentium | CPU Core<br>Frequency | Ratio | External<br>Bus<br>Clock | JP1 & JP2 | JP3 & JP4 | JP13      |

|------------------|-----------------------|-------|--------------------------|-----------|-----------|-----------|

| P54C 75          | 75MHz =               | 1.5X  | 50MHz                    | 1-2 & 1-2 | 2-3 & 2-3 | 1-2 & 5-6 |

| P54C 90          | 90MHz =               | 1.5x  | 60MHz                    | 1-2 & 1-2 | 1-2 & 2-3 | 1-2 & 3-4 |

| P54C 100         | 100MHz =              | 1.5x  | 66MHz                    | 1-2 & 1-2 | 2-3 & 1-2 | 3-4       |

| P54C 120         | 120MHz =              | 2x    | 60MHz                    | 2-3 & 1-2 | 1-2 & 2-3 | 1-2 & 3-4 |

| P54C 133         | 133MHz =              | 2x    | 66MHz                    | 2-3 & 1-2 | 2-3 & 1-2 | 3-4       |

| P54C 150         | 150MHz =              | 2.5x  | 60MHz                    | 2-3 & 2-3 | 1-2 & 2-3 | 1-2 & 3-4 |

| P54C 166         | 166MHz =              | 2.5x  | 66MHz                    | 2-3 & 2-3 | 2-3 & 1-2 | 3-4       |

| P54C 200         | 200MHz =              | 3x    | 66MHz                    | 1-2 & 2-3 | 2-3 & 1-2 | 3-4       |

| Intel<br>Pentium | CPU Core<br>Frequency | Ratio | External<br>Bus<br>Clock | JP1 & JP2 | JP3 & JP4 | JP13      |

|------------------|-----------------------|-------|--------------------------|-----------|-----------|-----------|

| PP/MT 150        | 150MHz =              | 2.5x  | 60MHz                    | 2-3 & 2-3 | 1-2 & 2-3 | 1-2 & 3-4 |

| PP/MT 166        | 166MHz =              | 2.5x  | 66MHz                    | 2-3 & 2-3 | 2-3 & 1-2 | 3-4       |

| PP/MT 200        | 200MHz =              | 3x    | 66MHz                    | 1-2 & 2-3 | 2-3 & 1-2 | 3-4       |

| PP/MT 233        | 200MHz =              | 3.5x  | 66MHz                    | 1-2 & 1-2 | 2-3 & 1-2 | 3-4       |

| Cyrix 6x86 | CPU Core<br>Frequency | Ratio | External<br>Bus<br>Clock | JP1 & JP2 | JP3 & JP4 | JP13      |

|------------|-----------------------|-------|--------------------------|-----------|-----------|-----------|

| P120+      | 100MHz                | 2x    | 50MHz                    | 1-2 & 1-2 | 2-3 & 2-3 | 1-2 & 5-6 |

| P150+      | 120MHz =              | 2x    | 60MHz                    | 2-3 & 1-2 | 1-2 & 2-3 | 1-2 & 3-4 |

| P166+      | 133MHz =              | 2x    | 66MHz                    | 2-3 & 1-2 | 2-3 & 1-2 | 3-4       |

| AMD K5 | CPU Core<br>Frequency | Ratio | External<br>Bus<br>Clock | JP1 & JP2 | JP3 & JP4 | JP13      |

|--------|-----------------------|-------|--------------------------|-----------|-----------|-----------|

| PR90   | 90MHz =               | 1.5x  | 60MHz                    | 1-2 & 1-2 | 1-2 & 2-3 | 1-2 & 3-4 |

| PR100  | 100MHz =              | 1.5x  | 66MHz                    | 1-2 & 1-2 | 2-3 & 1-2 | 3-4       |

| PR120  | 90MHz =               | 1.5x  | 60MHz                    | 1-2 & 1-2 | 1-2 & 2-3 | 1-2 & 3-4 |

| PR133  | 100MHz =              | 1.5x  | 66MHz                    | 1-2 & 1-2 | 2-3 & 1-2 | 3-4       |

| PR166  | 116MHz =              | 1.75x | 66MHz                    | 2-3 & 2-3 | 2-3 & 1-2 | 3-4       |

| AMD K6 | CPU Core<br>Frequency | Ratio | External<br>Bus<br>Clock | JP1 & JP2 | JP3 & JP4 | JP13 |

|--------|-----------------------|-------|--------------------------|-----------|-----------|------|

| PR166  | 166MHz =              | 2.5x  | 66MHz                    | 2-3 & 2-3 | 2-3 & 1-2 | 3-4  |

| PR200  | 200MHz =              | 3x    | 66MHz                    | 1-2 & 2-3 | 2-3 & 1-2 | 3-4  |

**Note:** Cyrix 6x86 and AMD K5 CPU use P-rating for the reference of CPU benchmark compared with INTEL P54C, their internal core frequency is not exactly equal to P-rating marked on the CPU. For example, Cyrix P166+ is 133MHz but performance is almost equal to P54C 166MHz and AMD PR133 is 100MHz but performance is almost equal to INTEL P54C 133MHz.

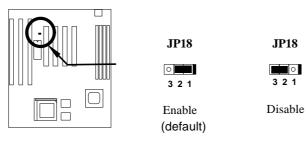

#### 2.2.3 Disabling the Onboard Super I/O Controller

| <u>JP18</u> | <b>Onboard Super I/O</b>    | The board is default to enable the onboard                                                                                                                                                                 |

|-------------|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1-2<br>2-3  | Enable (default)<br>Disable | Super I/O controller. In case you wish to use<br>an external I/O control card, you need to<br>disable the onboard I/O before using the<br>external I/O card. To disable it, set the jumper<br>JP18 to 2-3. |

### 2.2.4 Disabling the PS/2 Mouse Function

| <u>JP20</u> | PS/2 Mouse       |

|-------------|------------------|

| 1-2         | Enable (default) |

| 2-3         | Disable          |

|             |                  |

The PS/2 mouse function is normally enabled and occupies IRQ12. To reassign IRQ12 for other function, disable the PS/2 mouse function by setting the jumper **JP20** to 2-3.

Enable (default)

|   |   | 0 |  |

|---|---|---|--|

| 3 | 2 | 1 |  |

|   |   |   |  |

**JP20**

Disable

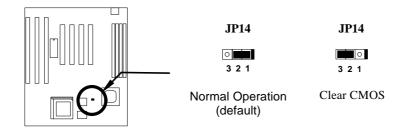

### 2.2.5 Clearing the CMOS

| <u>JP14</u> | <u>Clear CMOS</u> |

|-------------|-------------------|

| 1-2         | Normal operation  |

|             | (default)         |

| 2-3         | Clear CMOS        |

|             |                   |

You need to clear the CMOS if you forget your system password. To clear the CMOS, follow the procedures listed below:

#### The procedure to clear CMOS:

- 1. Turn off the system power.

- 2. Locate JP14 and short pins 2-3 for a few seconds.

- 3. Return **JP14** to its normal setting by shorting pins 1-2.

- 4. Turn on the system power.

- 5. Press DEL during bootup to enter the BIOS Setup Utility and specify a new password, if needed.

#### 2.2.6 Selecting the CPU Burst Mode

| <u>JP22</u> | CPU Burst Mode |  |  |

|-------------|----------------|--|--|

| 1-2         | Linear (Cyrix) |  |  |

2-3 Toggle (Intel/AMD)

**JP22** is used to select CPU burst mode of SIS chipset. For Cyrix CPU, JP22 must be set at 1-2 Linear Mode. For Intel and AMD CPU, JP22 must be set at 2-3 Toggle Mode.

JP22 3 2 1

Linear (Cyrix)

Toggle (Intel/AMD)

**JP22**

321

### 2.3 Connectors

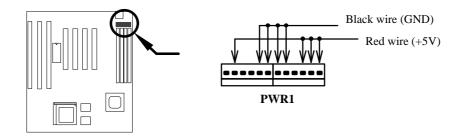

#### 2.3.1 Power Cable

A standard baby AT (PS/2) power supply has two cables with six wires on each. Plug in these cables to the onboard power connector in such a way that all the black wires are in the center. The power connector is marked as **PWR1** on the system board.

**Caution:** Make sure that the power supply is off before connecting or disconnecting the power cable.

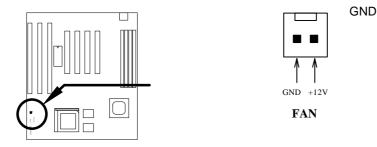

#### 2.3.2 CPU Fan

Plug in the fan cable to the two-pin fan connector onboard. The fan connector is marked  ${\bf FAN}$  on the system board.

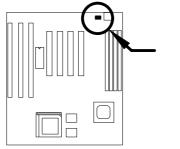

#### 2.3.3 PS/2 Mouse

To connect a PS/2 mouse, insert the PS/2 mouse bracket connector to **PS2 MS** on the system board. Then plug in the PS/2 mouse cable to the mouse port on the bracket.

| <u>Pin</u> | <b>Description</b> |

|------------|--------------------|

| 1          | MS DATA            |

| 2          | NC                 |

| 3          | GND                |

| 4          | +5V                |

| 5          | MS CLK             |

| 6          | NC                 |

|            |                    |

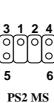

### 2.3.4 Serial Devices (COM1/COM2)

To support serial devices, insert the serial device connector into the serial port on the bracket. Plug in the 10-pin flat cable to the appropriate onboard connectors. The serial port 1 connector is marked as **COM1** and the serial port 2 connector is marked as **COM2** on the system board.

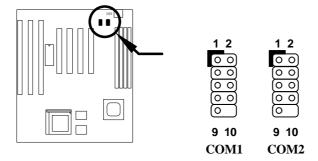

### 2.3.5 USB Device (optional)

You need a USB bracket to have your system to support additional USB device(s). To attach a USB bracket, simply insert the bracket cable to the onboard USB connector marked as **USB**.

| I | Pin | Description | <u>Pin</u> | Description |

|---|-----|-------------|------------|-------------|

|   | 1   | V0          | 2          | V1          |

|   | 3   | D0-         | 4          | D1-         |

|   | 5   | D0+         | 6          | D1+         |

|   | 7   | GND         | 8          | GND         |

|   | 9   | NC          | 10         | NC          |

|   |     |             |            |             |

### 2.3.6 Floppy Drive

Connect the 34-pin floppy drive cable to the floppy drive connector marked as **FDC** on the system board.

#### 2.3.7 Printer

Plug in the 26-pin printer flat cable to the onboard parallel connector marked as **PRINTER** on the board.

#### 2.3.8 IDE Hard Disk and CD ROM

This mainboard supports two 40 pin IDE connectors marked as **IDE1** and **IDE2**. IDE1 is also known as primary channel and IDE2 as secondary channel, each channel supports two IDE devices that makes total of four devices.

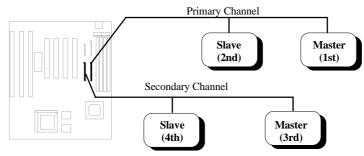

In order to work together, the two devices on each channel must be set differently to master and slave mode, either one can be hard disk or CDROM. The setting as master or slave mode depends on the jumper on your IDE device, please refer to your hard disk and CDROM manual accordingly.

Connect your first IDE hard disk to master mode of the primary channel. If you have second IDE device to install in your system, connect it as slave mode on the same channel, and the third and fourth device can be connected on secondary channel as master and slave mode respectively.

**Caution**: The specification of IDE cable is maximum 46cm (18 inches), make sure your cable does not excess this length.

**Caution:** For better signal quality, it is recommended to set far end side device to master mode and follow the suggested sequence to install your new device . Please refer to following figure.

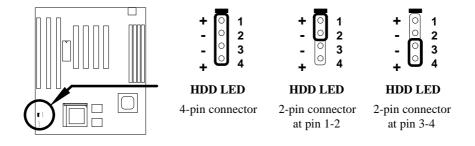

#### 2.3.9 Hard Disk LED

The HDD LED connector is marked as **HDD LED** on the board. This connector is designed for different type of housing, actually only two pins are necessary for the LED. If your housing has four pin connector, simply plug it in. If you have only two pin connector, please connect to pin 1-2 or pin 3-4 according to the polarity.

| <u>Pin</u> | <b>Description</b> |

|------------|--------------------|

| 1          | HDD LED            |

| 2          | GND                |

| 3          | GND                |

| 4          | HDD LED            |

|            |                    |

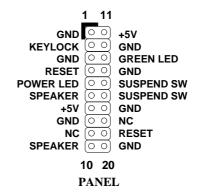

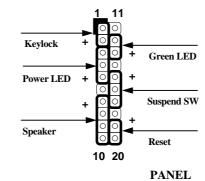

#### 2.3.10 Panel Connector

The Panel (multifunction) connector is a 20pin connector marked as **PANEL** on the board. Attach the power LED, keylock, speaker, reset switch, suspend switch, and green mode LED connectors to the corresponding pins as shown in the figure.

Some housings have a five-pin connector for the keylock and power LED Since power LED and keylock are aligned together, you can still use this kind of connector.

PANE

Other housings may have a 12-pin connector. If your housing has this type of connector, connect it to PANEL as shown in the figure. Make sure that the red wire of the connector is connected to +5V.

PANEL

**Note:** If your housing comes with Turbo switch and Turbo LED connectors, you may use these connectors for Suspend switch and Green mode LED functions, respectively.

**Note**: Pressing the Suspend switch allows you to manually force the system to suspend mode. However, this is possible only if the Power Management function in the BIOS Setup menu is enabled.

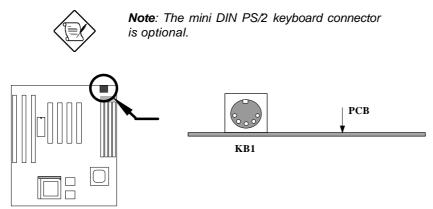

# 2.3.11 Keyboard

The onboard keyboard connector is a five-pin AT-compatible connector marked as KB1. The view angle of drawing shown here is from back panel of the housing.

#### 2.3.12 IrDA Connector

Serial port 2 can be configured to support wireless infrared module, with this module and application software such as Laplink, user can transfer files to or from laptops, notebooks, PDA and printers. This mainboard supports IrDA (115Kbps, 1 meter) as well as ASK-IR (19.2Kbps).

Install infrared module onto IrDA connector and enable infrared function from BIOS setup, make sure to have correct orientation when you plug onto IrDA connector.

| Pin | Description |  |  |

|-----|-------------|--|--|

| 1   | +5V         |  |  |

| 2   | NC          |  |  |

| 3   | IRRX        |  |  |

| 4   | GND         |  |  |

| 5   | IRTX        |  |  |

| 6   | +3.3V       |  |  |

Note: Onboard serial port 2 (COM2) will not be available afterIrDA connector is enabled.

0

1

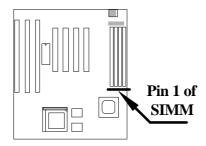

### 2.4 Configuring the System Memory

This mainboard has four 72 pin SIMM sockets (Single-in-line Memory Module) that allow you to install system memory from minimum 4MB up to maximum 256MB.

The SIMM supported by this mainboard can be identified by 4 kinds of factors:

- Size: single side, 1Mx32 (4MB), 4Mx32 (16MB), 16Mx32 (64MB), and double side, 1Mx32x2 (8MB), 4Mx32x2 (32MB), 16Mx32x2 (128MB).

- Speed: 60ns or 70ns access time

- Type: FPM (Fast page mode) or EDO (Extended data output)

- Parity: without parity (32 bit wide) or with parity (36 bit wide).

Because Pentium processor has 64 bit bus width, the four SIMM sockets are arranged in two banks of two sockets each, they are Bank0 and Bank1. Both SIMMs in each bank must be in the same size and type. It is allowed to have different speed and type in different bank, for example, 70ns FPM in one bank and 60ns EDO in another bank, in such case, each bank is independently optimized for maximum performance. The memory timing requires at least 70ns fast page mode DRAM chip, but for optimum performance, 60ns EDO DRAM is recommended.

**Warning**: The default memory timing setting is 60ns to obtain the optimal performance. Because of the specification limitation, 70ns SIMM is recommended to be used only for CPU external clock 60MHz.

**Tip:** EDO DRAM is designed to improve the DRAM read performance. Unlike traditional fast page mode, that tristates the memory output data to start the precharge activity, EDO DRAM holds the memory data valid until the next memory access cycle, which is similar to pipeline effect and reduces one clock state.

There is no jumper setting required for the memory size or type. It is automatically detected by the system BIOS. You can use any single side SIMM combination list below for, and the total memory size is to add them together, the maximum is 256MB.

| SIMM1 | SIMM2 | Subtotal of Bank0 |

|-------|-------|-------------------|

| None  | None  | 0MB               |

| 4MB   | None  | 4MB               |

| 8MB   | None  | 8MB               |

| 16MB  | None  | 16MB              |

| 32MB  | None  | 32MB              |

| 64MB  | None  | 64MB              |

| 4MB   | 4MB   | 8MB               |

| 8MB   | 8MB   | 16MB              |

| 16MB  | 16MB  | 32MB              |

| 32MB  | 32MB  | 64MB              |

| 64MB  | 64MB  | 128MB             |

| 128MB | 128MB | 256MB             |

| SIMM3 | SIMM4 | Subtotal of Bank1 |

|-------|-------|-------------------|

| None  | None  | 0MB               |

| 4MB   | 4MB   | 8MB               |

| 8MB   | 8MB   | 16MB              |

| 16MB  | 16MB  | 32MB              |

| 32MB  | 32MB  | 64MB              |

| 64MB  | 64MB  | 128MB             |

| 128MB | 128MB | 256MB             |

#### Total Memory Size = Subtotal of Bank0 + Subtotal of Bank1

**Caution:** Make sure that you install the same SIMM type and size for each bank.

The driving capability of new generation chipset is limited because the lack of memory buffer (to improve performance). This makes DRAM chip count an important factor to be taking into consideration when you install SIMM. Unfortunately, there is no way that BIOS can identified the correct chip count, you need to calculate the chip count by yourself. The simple rule is: By visual inspection, use only SIMM with chip count less than 24 chips.

**Warning**: Do not install any SIMM that contains more than 24 chips. SIMMs contain more than 24 chips exceed the chipset driving specification. Doing so may result in unstable system behavior.

*Tip:* The SIMM chip count can be calculated by following example:

- 1. For 32 bit non-parity SIMM using 1M by 4 bit DRAM chip, 32/4=8 chips.

- 2. For 36 bit parity SIMM using 1M by 4 bit DRAM chip, 36/4=9 chips.

- 3. For 36 bit parity SIMM using 1M by 4 bit and 1M by 1 bit DRAM, the chip count will be 8 data chips(8= 32/4) plus 4 parity chips(4=4/1), total is 12 chips.

#### Following table list the recommended DRAM combinations:

| SIMM<br>Data chip | SIMM<br>Parity chip | Bit size<br>per side | Single/<br>Double<br>side | Chip<br>count | SIMM<br>size | Recommended |

|-------------------|---------------------|----------------------|---------------------------|---------------|--------------|-------------|

| 1M by 4           | None                | 1Mx32                | x1                        | 8             | 4MB          | Yes         |

| 1M by 4           | None                | 1Mx32                | x2                        | 16            | 8MB          | Yes         |

| 1M by 4           | 1M by 1             | 1Mx36                | x1                        | 12            | 4MB          | Yes         |

| 1M by 4           | 1M by 4             | 1Mx36                | x1                        | 9             | 4MB          | Yes         |

| 1M by 4           | 1M by 4             | 1Mx36                | x2                        | 18            | 8MB          | Yes         |

| 1M by 16          | None                | 1Mx32                | x1                        | 2             | 4MB          | Yes         |

| 1M by 16          | None                | 1Mx32                | x2                        | 4             | 8MB          | Yes         |

| 1M by 16          | 1M by 4             | 1Mx36                | x1                        | 3             | 4MB          | Yes         |

| 1M by 16          | 1M by 4             | 1Mx36                | x2                        | 6             | 8MB          | Yes         |

| 4M by 4           | None                | 4Mx32                | x1                        | 8             | 16MB         | Yes         |

| 4M by 4           | None                | 4Mx32                | x2                        | 16            | 32MB         | Yes         |

| 4M by 4           | 4M by 1             | 4Mx36                | x1                        | 12            | 16MB         | Yes         |

| 4M by 4           | 4M by 1             | 4Mx36                | x2                        | 24            | 32MB         | Yes         |

| SIMM<br>Data chip | SIMM<br>Parity chip | Bit size<br>per side | Single/<br>Double<br>side | Chip<br>count | SIMM<br>size | Recommended          |

|-------------------|---------------------|----------------------|---------------------------|---------------|--------------|----------------------|

| 16M by 4          | None                | 16Mx32               | x1                        | 8             | 64MB         | Yes, but not tested. |

| 16M by 4          | None                | 16Mx32               | x2                        | 16            | 128MB        | Yes, but not tested. |

| 16M by 4          | 16M by 4            | 16Mx36               | x1                        | 9             | 64MB         | Yes, but not tested. |

| 16M by 4          | 16M by 4            | 16Mx36               | x2                        | 18            | 128MB        | Yes, but not tested. |

**Warning**: 64MB SIMMs using 16M by 4 bit chip (64M bit technology) are not available in the market and are not formally tested by AOpen quality test department yet. However they are supported by design specification of chipset and they will be tested as soon as they are available. Note that 64MB SIMMs using 16M by 1 bit chip (16M bit technology) have chip count exceed 24 and are strongly not recommended.

**Tip:** 8 bit = 1 byte, 32 bit = 4 byte. The SIMM size is represented by number of data byte (whether with or without parity), for example, the size of single side SIMM using 1M by 4 bit chip is 1Mx32 bit, that is,  $1M \times 4$  byte = 4MB. For double side SIMM, simply multiply it by 2, that is, 8MB.

| SIMM<br>Data chip | SIMM<br>Parity chip | Bit size<br>per side | Single/<br>Double<br>side | Chip<br>count | SIMM<br>size | Recommended |

|-------------------|---------------------|----------------------|---------------------------|---------------|--------------|-------------|

| 1M by 1           | None                | 1Mx32                | x1                        | 32            | 4MB          | No          |

| 1M by 1           | 1M by 1             | 1Mx36                | x1                        | 36            | 4MB          | No          |

| 1M by 4           | 1M by 1             | 1Mx36                | x2                        | 24            | 8MB          | No          |

| 4M by 1           | None                | 4Mx32                | x1                        | 32            | 16MB         | No          |

| 4M by 1           | 4M by 1             | 4Mx36                | x1                        | 36            | 16MB         | No          |

| 16M by 1          | None                | 16Mx32               | x1                        | 32            | 64MB         | No          |

| 16M by 1          | 16M by 1            | 16Mx36               | x1                        | 36            | 64MB         | No          |

#### Following table are possible DRAM combinations that is **NOT** recommended: