# **SUPER®**

440LX Chipset

AMI BIOS

REFERENCE MANUAL

Revision 1.0

The information in this User's Manual has been carefully reviewed and is believed to be accurate. The vendor assumes no responsibility for any inaccuracies that may be contained in this document, makes no commitment to update or to keep current the information in this manual, or to notify any person or organization of the updates.

The manufacturer reserves the right to make changes to the product described in this manual at any time and without notice. This product, including software, if any, and documentation may not, in whole or in part, be copied, photocopied, reproduced, translated or reduced to any medium or machine without prior written consent.

IN NO EVENT WILL THE MANUFACTURER BE LIABLE FOR DIRECT, INDIRECT, SPECIAL, INCIDENTAL, OR CONSEQUENTIAL DAMAGES ARISING FROM THE USE OR INABILITY TO USE THIS PRODUCT OR DOCUMENTATION, EVEN IF ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. IN PARTICULAR, THE VENDOR SHALL NOT HAVE LIABILITY FOR ANY HARDWARE, SOFTWARE, OR DATA STORED OR USED WITH THE PRODUCT, INCLUDING THE COSTS OF THE REPAIRING, REPLACING, OR RECOVERING SUCH HARDWARE, SOFTWARE, OR DATA.

Copyright @ 1997 by SUPERMICRO COMPUTER INC. All rights reserved.

Printed in the United States of America.

Unless you request and receive written permission from the manufacturer, you may not copy any part of this document.

All products and company names mentioned are trademarks or registered trademarks of their respective holders.

Do not upgrade the BIOS unless you are notified to do so. Please call technical support first before upgrading the boot-block BIOS.

SUPER BBS # (408) 895-2022 (24 hours)

Baud Rate: 1200-14400 bps, Data Bits: 8, Stop Bit: 1, Parity: None

### **Table of Contents**

| Ch  | pter 1: AMI BIOS                     |   |

|-----|--------------------------------------|---|

| 1-1 | Introduction                         |   |

|     | System BIOS1-                        | 1 |

|     | Configuration Data1-                 | 1 |

|     | How Data Is Configured1-             | 1 |

|     | POST Memory Test1-                   | 2 |

| 1-2 | BIOS Features1-                      | 2 |

|     | BIOS Configuration Summary Screen 1- | 3 |

| Ch  | pter 2: Running Setup                |   |

| 2-1 | Setup                                |   |

|     | 2-1-1 Standard Setup2-               | 1 |

|     | 2-1-2 Advanced Setup 2-              | 3 |

|     | 2-1-3 Chipset Setup 2-               | 8 |

|     | 2-1-4 Power Management 2-1           | 5 |

|     | 2-1-5 PCI/PnP Setup 2-1              | 8 |

|     | 2-1-6 Peripheral Setup 2-2           | 2 |

| 2-2 | Security Setup                       |   |

|     | 2-2-1 Supervisor/User2-2             | 5 |

|     | 2-2-2 Anti-Virus                     | 6 |

| 2-3 | Utility Setup                        |   |

|     | 2-3-1 Language2-2                    | 6 |

|     | 2-3-2 Detect IDE2-2                  | 6 |

| 2-4 | Default Setting                      |   |

|     | 2-4-1 Optimal Default2-2             | 2 |

|     | 2-4-2 Fail-Safe Default2-2           | 2 |

| Appendix A: | Hard Disk Error Messages                | A-1 |

|-------------|-----------------------------------------|-----|

| Appendix B: | BIOS Hard Disk Drive Types              | B-1 |

| Appendix C: | BIOS Error Beep Codes                   | C-1 |

| Appendix D: | AMI BIOS POST Diagnostic Error Messages | D-1 |

| Appendix F: | BIOS Non-Fatal Error Messages           | E-1 |

PRINTED IN U.S.A.

# Chapter 1 AMI BIOS

#### 1-1 Introduction

This chapter describes the AMIBIOS for the Intel 440FX chipset which is designed for Intel Pentium® Pro 150/166/180/200 MHz and Pentium II 233/266/300 MHz processors. The AMI ROM BIOS is stored in the Flash EEPROM and is easily upgraded using a floppy disk-based program.

#### **System BIOS**

The BIOS is the basic input output system used in all IBM® PC,  $XT^{TM}$ ,  $AT^{\otimes}$ , and PS/2® compatible computers. The WinBIOS is a high-quality example of a system BIOS.

#### **Configuration Data**

AT-compatible systems, also called ISA (Industry Standard Architecture) must have a place to store system information when the computer is turned off. The original IBM AT had 64 bytes of non-volatile memory storage in CMOS RAM. All AT-compatible systems have at least 64 bytes of CMOS RAM, which is usually part of the Real Time Clock. Many systems have 128 bytes of CMOS RAM.

#### **How Data Is Configured**

AMIBIOS provides a Setup utility in ROM that is accessed by pressing <Del> at the appropriate time during system boot. Setup configures data in CMOS RAM.

#### **POST Memory Test**

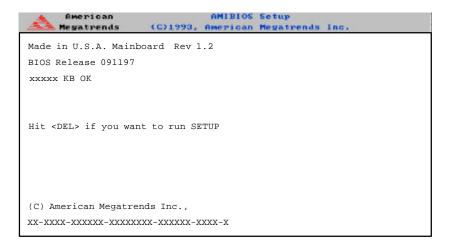

Normally, the only visible POST routine is the memory test. The screen that appears when the system is powered on is shown below.

An AMIBIOS Identification string is displayed at the left bottom corner of the screen, below the copyright message.

#### 1-2 BIOS Features

- supports Plug and Play V1.0A and DMI 2.0

- supports Intel PCI 2.1 (Peripheral Component Interconnect) local bus specification

- supports EDO (Extended Data Out), ECC and FPM DRAM

- supports ECC (Error Checking and Correction)

- supports Flash ROM

#### **BIOS Configuration Summary Screen**

AMIBIOS displays a screen that looks similar to the following when the POST routines complete successfully.

| AMIBIOS System  | Configuration (C) 19 | 85-1994 American Meg | gatrends Inc., |

|-----------------|----------------------|----------------------|----------------|

| Main Processor  | : Pentium(tm) II     | Base Memory Size     | : 640 KB       |

| Math Processor  | : Built-In           | Ext. Memory Size     | : 31744 KB     |

| Floppy Drive A: | : 1.2 MB, 5%         | Display Type         | : VGA/EGA      |

| Floppy Drive B: | : 1.44 MB, 3%        | Serial Port(s)       | : 3F8,2F8      |

| AMI-BIOS Date   | : 7/15/95            | Parallel Port(s)     | : 378          |

| Processor Clock | : 200MHz             | Power Management     | : APM, SMI     |

# Chapter 2 Running Setup

The WinBIOS Setup options described in this section are selected by choosing the appropriate high-level icon from the Standard Setup screen. All displayed icons are described in this section, although the screen display is often all you need to understand how to set the option.

#### 2-1 Setup

#### 2-1-1 Standard Setup

Pri Master Pri Slave Sec Master Sec Slave

Choose these icons to configure the hard disk drive. When you click on an icon, the following parameters are listed: *Type, LBA/Large Mode, Block Mode, 32Bit Mode, and PIO Mode.* All parameters relate to IDE drives except *Type.*

If the hard disk drive to be configured is an IDE drive, select the appropriate drive icon, choose the *Type* parameter and select *Auto*. The BIOS will automatically detect the IDE drive parameters and display them. Click on the OK button to accept these parameters.

Click on *LBA/Large Mode* and choose *On* to enable support for IDE drives with capacities greater than 528MB. Click on *Block Mode* and choose *On* to support IDE drives that use Block Mode. Click on *32Bit Mode* and click on *On* to support IDE drives that permit 32-bit accesses.

To configure an old MFM hard disk drive, you must know the drive parameters (number of heads, number of cylinders, number of sectors, the starting write precompensation cylinder, and drive capacity). Select the hard disk drive type (1-46). Refer to Appendix B in this manual for a list of the various hard disk drive types. Select *User* in the *Type* field if the drive parameters on your MFM drive do not match any of the drive type in Appendix B.

#### **Entering Drive Parameters**

You can also enter the hard disk drive parameters. The drive parameters are:

| Parameter                | Description                                                                                                                                                                                                                                                                                                                                                            |

|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Туре                     | The number for a drive with certain identification parameters.                                                                                                                                                                                                                                                                                                         |

| Cylinders                | The number of cylinders in the disk drive.                                                                                                                                                                                                                                                                                                                             |

| Heads                    | The number of heads.                                                                                                                                                                                                                                                                                                                                                   |

| Write<br>Precompensation | The size of a sector gets progressively smaller as the track diameter diminishes. Yet each sector must still hold 512 bytes. Write precompensation circuitry on the hard disk compensates for the physical difference in sector size by boosting the write current for sectors on inner tracks. This parameter is the track number where write precompensation begins. |

| Landing Zone             | This number is the cylinder location where the heads will normally park when the system is shut down.                                                                                                                                                                                                                                                                  |

| Sectors                  | The number of sectors per track. MFM drives have 17 sectors per track. RLL drives have 26 sectors per track. ESDI drives have 34 sectors per track. SCSI and IDE drive may have even more sectors per track.                                                                                                                                                           |

| Capacity                 | The formatted capacity of the drive is (Number of heads) $x$ (Number of cylinders) $x$ (Number of sectors per track) $x$ (512 bytes per sector)                                                                                                                                                                                                                        |

#### Date and Time Configuration

Select the Standard option. Select the *Date/Time* icon. The current values for each category are displayed. Enter new values through the keyboard.

#### Floppy A Floppy B

Choose the Floppy Drive A or B icon to specify the floppy drive type. The settings are 360 KB 5¼ inch, 1.2 MB 5¼ inch, 720 KB 3½ inch, 1.44 MB 3½ inch, 2.88 MB 3½ inch or Not Installed.

#### 2-1-2 Advanced Setup

#### **Quick Boot**

Set this option to *Enabled* to permit AMIBIOS to boot within 5 seconds. The settings are *Disabled* or *Enabled*. The Optimal and Fail-Safe default settings are *Disabled*.

1st Boot Device 2nd Boot Device 3rd Boot Device

The options for 1st Boot Device are *Disabled*, *IDE-0*, *IDE-1*, *IDE-2*, *IDE-3*, *Floptical*, or *SCSI*. The options for 2nd Boot Device are *Disabled*, *Floppy*, *SCSI*, or *Floptical*. The options for 3rd Boot Device are *Disabled*, *Floptical*, *SCSI*, or *CDROM*.

The *Disabled* option means that setup will not be considered during the boot process. Floppy can be selected only as 2nd boot device. CDROM can be selected only as 3rd boot device. The same device cannot be chosen more than once. For example, if *Floptical* is chosen as 2nd boot device, it cannot be chosen as any other boot device.

IDE-0, IDE-1, IDE-2, IDE-3 are the four hard disks than can be installed by the BIOS. IDE-0 is the first hard disk installed by the BIOS, IDE-1 is the second hard disk, and so on. For example, if the system has a hard disk connected to Primary Slave and another hard disk to Secondary Master, then IDE-0 will be referred to as the hard disk connected to Primary Slave and IDE-1 will be referred to as the hard disk connected to the Secondary Master. IDE-2 and IDE-3 are not present. Note that the order of the initialization of the devices connected to the primary and secondary channels are Primary Master first, Primary Slave second, Secondary Master third, and Secondary Slave fourth.

The BIOS will attempt to read the boot record from 1st, 2nd, and 3rd boot device in the selected order until it is successful in reading the booting record. The BIOS will not attempt to boot from any device which is not selected as the boot device.

#### Try Other Boot Device

This option controls the action of the BIOS if all the selected boot devices failed to boot. The settings for this option are Yes or No. If Yes is selected and all the selected boot devices failed to boot, the BIOS will try to boot from the other boot devices (in a predefined sequence) which are present but not selected as boot devices in the setup (and hence not yet been tried for booting). If selected as No and all selected boot devices failed to boot, the BIOS will try not to boot from the other boot devices which may be present but not selected as boot devices in setup. The Optimal and Fail-Safe default settings are Yes.

#### Initial Display Mode

This option determines the display screen with which the POST is going to start the display. If selected as *BIOS*, the POST will start with the normal sign-on message screen. If *Silent* is selected, the POST will start with the silent screen. The settings for this option are *BIOS* or *Silent*. The Optimal and Fail-Safe default settings are *BIOS*.

#### Display Mode at Add-on ROM Init

This option determines the display mode during add-on ROM (except Video add-on ROM) initialization. The settings for this option are *Force BIOS* or *Keep Current*. If selected as *Force BIOS*, the POST will force the display to be changed to BIOS mode before giving control to any add-on ROM. If no add-on ROM is found, then the current display mode will remain unchanged even if this setup question is selected as *Force BIOS*. If selected as *Keep Current*, then the current display mode will remain unchanged. The Optimal and Fail-Safe default settings are *Force BIOS*.

#### Floppy Access Control

The settings for this option are *Read-Write* or *Read-Only*. The Optimal and Fail-Safe default settings are *Read-Write*.

#### Hard Disk Access Control

The settings for this option are *Read-Write* or *Read-Only*. The Optimal and Fail-Safe default settings are *Read-Write*.

#### S.M.A.R.T. for Hard Disks

S.M.A.R.T. (Self-Monitoring, Analysis and Reporting Technology) is a technology developed to manage the reliability of the hard disk by predicting future device failures. The hard disk needs to be S.M.A.R.T. capable. The settings for this option are *Disabled* or *Enabled*. The Optimal and Fail-Safe default settings are *Disabled*.

#### **Boot Up Num-Lock**

When this option is set to On, the BIOS turns off the Num Lock key when the system is powered on. This will enable the end user to use the arrow keys on both the numeric keypad and the keyboard. The settings are On or Off. The Optimal and Fail-Safe default settings are On.

#### PS/2 Mouse Support

When this option is set to *Enabled*, AMIBIOS supports a PS/2-type mouse. The settings are *Enabled* or *Disabled*. The Optimal and Fail-Safe default settings are *Enabled*.

#### **Primary Display**

This option specifies the type of display adapter card installed in the system. The settings are VGA/EGA, CGA40x25, CGA80x25, Mono, or Absent. The Optimal and Fail-Safe default settings are VGA/EGA.

#### Password Check

This option enables the password check option every time the system boots or the end user runs WinBIOS Setup. If *Always* is chosen, a user password prompt appears every time the computer is turned on. If *Setup* is chosen, the password prompt appears if WinBIOS Setup is executed. The Optimal and Fail-Safe default settings are *Setup*.

#### Boot to OS/2

If DRAM size is over 64M, set this option to Yes to permit AMIBIOS to run with IBM OS/2. The settings are No or Yes. The Optimal and Fail-Safe default settings are No.

#### **CPU MicroCode Updation**

Set this option to *Enabled* to allow the CPU microcode to be updated online at any time. The settings for this option are *Disabled* or *Enabled*. The Optimal and Fail-Safe default settings are *Enabled*.

#### Internal Cache

This option is for enabling or disabling the internal cache memory. The settings for this option are *Disabled*, *WriteThru* or *WriteBack*. The Optimal and Fail-Safe default settings are *WriteBack*.

#### System Bios Cacheable

AMIBIOS always copies the system BIOS from ROM to RAM for faster execution. Set this option to *Enabled* to permit the contents of F0000h RAM memory segment to be written to and read from cache memory. The settings are *Disabled* or *Enabled*. The Optimal default setting is *Enabled*. The Fail-Safe default setting is *Disabled*.

C000, 16K Shadow C400, 16K Shadow

These options specify how the contents of the video ROM are handled. The settings are: *Disabled*, *Cached* or *Enabled*. When set to *Cached*, the contents of the video ROM area from C0000h-C7FFFh are not only copied from ROM to RAM, the contents of the C0000h-C7FFFh RAM can be written to or read from cache memory. The Optimal and Fail-Safe default settings are *Cached*.

C800, 16K Shadow CC00, 16K Shadow D000, 16K Shadow D400, 16K Shadow D800, 16K Shadow DC00, 16K Shadow

These options specify how the contents of the adaptor ROM named in the option title are handled. The ROM area that is not used by ISA adapter cards will be allocated to PCI adapter cards. The settings are: *Disabled, Cached* or *Enabled*. The Optimal and Fail-Safe default settings are *Disabled*.

#### 2-1-3 Chipset Setup

#### **USB Function**

Set this option to *Enabled* to enable the USB (Universal Serial Bus) functions. The settings for this option are *Enabled* or *Disabled*. The Optimal and Fail-Safe default settings are *Disabled*.

#### USB KB/Mouse Legacy Support

Set this option to *Enabled* to enable the USB keyboard and mouse. The settings for this option are *Enabled* or *Disabled*. The Optimal and Fail-Safe default settings are *Disabled*.

#### SDRAM Autosizing Support

If the Serial Presence Detect (SPD) is not available, then the BIOS will try to detect the memory and do the autosizing. The settings for this option are *Enabled* or *Disabled*. The Optimal and Fail-Safe default settings are *Disabled*.

#### EDO DRAM Speed (ns)

This option should be set according to the speed of the EDO DRAM in the system. The value of this option determines how the EDO DRAM timings should be programmed in the chipset. The settings for this option are *Auto*, *Manual*, *50*, *60* or *70*. The Optimal and Fail-Safe default settings are *Auto*.

#### **EDO Read Burst Timing**

Burst mode EDO have internal column counters. Because of this, they do not need to accept row address and starting column address from the EDO memory controller. This eliminates the setup and hold time for the second and subsequent column addresses.

It also improves the EDO Read access time. The settings for this option are x333 or x222. The Optimal and Fail-Safe default settings are x333.

#### **EDO Write Burst Timing**

Burst mode EDO have internal column counters. Because of this, they do not need to accept row address and starting column address from the EDO memory controller. This eliminates the setup and hold time for the second and subsequent column addresses. It also improves the EDO Write access time. The settings for this option are x333 or x222. The Optimal and Fail-Safe default settings are x333.

#### EDO RAS Precharge

Memory needs to be recharged to ensure the information stored isn't lost. This feature eliminates the RAS (Row Address Strobe) recharge time since memory must always be addressed in the order of Row first, then Column. The settings for this option are 4 Clks or 3 Clks. The Optimal and Fail-Safe default settings are 4 Clks.

#### **EDO RAS to CAS**

As previously described, memory must always be addressed in the order of Row, then Column. The EDO RAS to CAS feature sets the timing delay between Row addressing and Column addressing. The settings for this option are 3 Clks or 2 Clks. The Optimal and Fail-Safe default settings are 3 Clks.

#### MA Waitstate

Use this feature to configure the memory address wait state. The settings for this option are *Slow* or *Fast*. The Optimal and Fail-Safe default settings are *Slow*.

#### SDRAM Timing Latency

Use this feature to select the SDRAM timing delay. The settings for this option are *Manual* or *Auto*. The Optimal and Fail-Safe default settings are *Auto*.

#### SDRAM RAS to CAS

The settings for this option are 3 Clks or 2 Clks. The Optimal and Fail-Safe default settings are 3 Clks.

#### SDRAM CAS Lat

This feature is for the Column Address Strobe latency. The settings for this option are 3 *Clks* or 2 *Clks*. The Optimal and Fail-Safe default settings are 3 *Clks*.

#### SDRAM RAS Precharge

This feature is for the SDRAM Row Address Strobe delay. The settings for this option are 3 Clks or 2 Clks. The Optimal and Fail-Safe default settings are 3 Clks.

#### VGA Frame Buffer USWC

USWC is a memory cycle type that stands for Uncacheable Speculative Write Combining. The settings are: *Disabled* or *Enabled*. The Optimal and Fail-Safe default settings are *Disabled*.

#### PCI Frame Buffer USWC

When *Enabled*, the PCI frame buffer address and length are divided into 2. The value is then programmed into the processor Variable MTRR (3) with the value for USWC (01h). The settings are: *Disabled* or *Enabled*. The Optimal and Fail-Safe default settings are *Disabled*.

#### DRAM Integrity Mode (ECC)

Set this option to *Enabled* to enable ECC DRAM integrity mode. ECC allows critical system to detect and correct memory errors, while normal parity generator/checker can only detect such memory errors. The settings are: *Non ECC, EC only* or *ECC*. The Optimal and Fail-Safe default settings are *Non ECC*.

#### Fixed Memory Hole

This option allows a memory hole to be specified for either the 512-640K region or the 15-16M region. The settings for this option are *Disabled*, *512-640KB* or *15-16MB*. The Optimal and Fail-Safe default settings are *Disabled*.

### Type F DMA Buffer Control 1 Type F DMA Buffer Control 2

Instead of 8 sysclock, Type F DMA only requires 3 sysclock to finish the data transfer. These two options are device dependent. The settings are *Channel 0*, *Channel 1*, *Channel 2*, *Channel 3*, *Channel 5*, *Channel 6*, *Channel 7* or *Disabled*. The Optimal and Fail-Safe default settings are *Disabled*.

DMA-0 Type DMA-1 Type DMA-2 Type DMA-3 Type DMA-5 Type DMA-6 Type DMA-7 Type

The settings for these Direct Memory Access channels are *Normal ISA*, *PC/PCI* or *Distributed*. The Optimal and Fail-Safe default settings are *Normal ISA*.

#### AGP Aperture Size

This register determines the effective size of the Graphics Aperture used in the particular PAC configuration. This register can be updated by the PAC-specific BIOS configuration sequence before PCI standard bus enumeration sequence takes place. If the register is not updated, a default value selects aperture of maximum size (i.e., 256 MB). The settings are: 4 MB, 8 MB, 16 MB, 32 MB, 64 MB, 128 MB or 256 MB. The Optimal and Fail-Safe default settings are 256 MB.

#### System Type

The settings are: Auto, DP or UP. The Optimal and Fail-Safe default settings are Auto.

#### USWC Write I/O Post

Use this feature for the WC Write Post During I/O Bridge Access Enable (WPIO). When set to *Enabled*, posting of WC transactions to PCI occur, even if the I/O bridge has been granted access to the PCI bus via corresponding arbitration and buffer management protocol. USWC Write posting should only be enabled if a USWC region is located on the PCI bus. The settings are: *Auto*, *Disabled* or *Enabled*. The Optimal and Fail-Safe default settings are *Auto*.

MECC Buf. Strength MD Buf. Strength WE Buf. Strength Max Buf. Strength MA Buf. Strength SCAS3 Buf. Strength SCAS2:0 Buf. Strength SRAS3 Buf. Strength SRAS2:0 Buf. Strength DQMX5 Buf. Strength DQMX1 Buf. Strength CSX Buf. Strength CS7:6 Buf. Strength CS5:0 Buf. Strength

The above features control the memory buffer strength. They are used to program the various DRAM interface signal buffer strengths, based on memory configuration, DRAM type (EDO or SDRAM), DRAM density (x4, x8, x16, or x32), DRAM technology (16 Mb or 64 Mb), and rows populated. The Optimal and Fail-Safe default settings are *Auto*.

#### PAC Bus SERR#

When set to *Enabled*, the PAC's SERR# signal driver is enabled and SERR# is asserted for all relevant bits set in the ERRSTS and PCISTS as controlled by the corresponding bits of the ERRCMD register. When *Disabled*, SERR# is never driven by the PAC. The settings are: *Disabled* or *Enabled*. The Optimal and Fail-Safe default settings are *Enabled*.

#### AGP Common SERR#

The settings are: *Disabled* or *Enabled*. The Optimal and Fail-Safe default settings are *Enabled*.

#### AGP System Error Forwarding

The settings are: *Disabled* or *Enabled*. The Optimal and Fail-Safe default settings are *Enabled*.

#### AGP Parity Error Response

The settings are: Disabled or Enabled. The Optimal and Fail-Safe default settings are Enabled.

#### IRQ12

The settings are: Auto, Standard or Mouse. The Optimal and Fail-Safe default settings are Auto.

#### PIIX4 SERR#

Use this feature for the SERR# generation due to delayed transaction time-out enable. The settings are: *Disabled* or *Enabled*. The Optimal and Fail-Safe default settings are *Disabled*.

#### USB Passive Release Enable

When set to *Enabled*, it allows the PIIX4 to use Passive Release while transferring control information or data for USB transactions. When *Disabled*, PIIX4 will perform PCI accesses for USB without using Passive Release. The settings are: *Disabled* or *Enabled*. The Optimal and Fail-Safe default settings are *Enabled*.

#### PIIX4 Passive

Use the PIIX4 Passive feature to enable the Passive Release mechanism encoded on the PHOLD# signal when PIIX4 is a PCI master. The settings are: *Disabled* or *Enabled*. The Optimal and Fail-Safe default settings are *Enabled*.

#### PIIX4 Delayed Transaction

Use this feature to enable the Delayed Transaction mechanism when the PIIX4 is the target of a PCI transaction. The settings are: Disabled or Enabled. The Optimal and Fail-Safe default settings are Enabled.

#### Master Lat. Timer

Master Latency Timer is an 8-bit register that controls the amount of time the PAC, as a PCI bus master, can burst data on the PCI bus. The count value is an 8 bit quantity. However, MLT[2:0] are 0 when determining the count value. The PAC's MLT is used to guarantee to the PCI agents (other than PAC) a minimum amount of the system resources. The settings are in increments with an Optimal and Fail-Safe default setting of 40H.

#### MTT

Multi-Transaction Timer is an 8-bit register that controls the amount of time that the PAC's arbiter allows a PCI initiator to perform multiple back-to-back transactions on the PCI bus. The PAC's MTT mechanism is used to guarantee the fair share of the PCI bandwidth to an initiator that performs multiple back-to-back transactions to fragmented memory ranges (and as a consequence it cannot use long burst transfers). The settings are in increments with an Optimal and Fail-Safe default setting of 20H.

#### 2-1-4 Power Management

#### ACPI Aware OS

Use this feature if your operating system supports Microsoft's Advanced Configuration and Power Interface (ACPI) standard. The settings are: Yes or No. The Optimal and Fail-Safe default settings are No.

#### Power Management/APM

This power conservation feature is specified by Intel and Microsoft INT 15h Advance Power Management BIOS functions. The settings are: *Disabled* or *Enabled*. When this feature is set to *Enabled*, the

system power conservation features are controlled by the system BIOS, not by the operation system. The Optimal and Fail-Safe default settings are *Disabled*.

#### **Power Button Function**

This feature is used to select the functionality of the power supply's power button. The settings are: *Suspend* or *On/Off*. The Optimal and Fail-Safe default settings are *On/Off*.

#### Instant on Support

Instant-on is one of ACPI's standard feature. The system comes back on instantly from ACPI's SoftOff state. The settings are: *Disabled* or *Enabled*. The Optimal and Fail-Safe default settings are *Disabled*.

#### Green PC Monitor Power State

This option specifies the power state that the green PC-compliant video monitor enters when AMIBIOS places it in a power savings state after the specified period of display inactivity has expired. The settings are *Off*, *Standby*, or *Suspend*. The Optimal and Fail-Safe default settings are *Standby*.

#### Video Power Down Mode

This option specifies the power conserving state that the VGA video subsystem enters after the specified period of display inactivity has expired. The settings are *Disabled*, *Standby*, or *Suspend*. The Optimal and Fail-Safe default settings are *Disabled*.

#### Hard Disk Power Down Mode

This option specifies the power conserving state that the hard disk drive enters after the specified period of hard drive inactivity has expired. The settings are *Disabled*, *Standby*, or *Suspend*. The Optimal and Fail-Safe default settings are *Disabled*.

#### Hard Disk Timeout (Minutes)

This option specifies the length of a period of hard disk drive inactivity. When this length of time expires, the computer enters power-conserving state specified in the Hard Disk Power Down Mode option. The settings are *Disabled* and 1 Min through 15 Min in 1 minute intervals. The Optimal and Fail-Safe default settings are *Disabled*.

#### Standby/Suspend Timer Unit

This allows you to set the standby time out and suspend time out timer unit. The settings are 32 secs, 4 msec, 4 min or 4 sec. The Optimal and Fail-Safe default settings are 4 min.

#### Standby Timeout

This option specifies the length of a period of system inactivity while in full power on state. When this length of time expires, the computer enters standby power state. The settings are *Disabled* and *1 Min through 15 Min in 1 minute intervals*. The Optimal and Fail-Safe default settings are *Disabled*.

#### Suspend Timeout (Minutes)

This option specifies the length of a period of system inactivity while in standby state. When this length of time expires, the computer enters suspend power state. The settings are *Disabled* and *1 Min through 15 Min in 1 minute intervals*. The Optimal and Fail-Safe default settings are *Disabled*.

#### Slow Clock Ratio

The value of the slow clock ratio indicates the percentage of time the STPCLK# signal is asserted while in the thermal throttle mode. The settings are 0-12.5%, 12.5-25%, 25-37.5%, 37.5%-50%, 50%-62.5%, 62.5-75%, and 75%-87.5%. The Optimal and Fail-Safe default settings are 50%-62.5%.

#### **Display Activity**

This option specifies if AMIBIOS is to monitor display activity for power conservation purposes. When this option is set to *Monitor* and there is no display activity for the length of time specified in the Standby Timeout (Minute) option, the computer enters a power savings state. The settings are *Monitor* or *Ignore*. The Optimal and Fail-Safe default settings are *Ignore*.

```

Device 6 (Serial port 1)

Device 7 (Serial port 2)

Device 8 (Parallel port)

Device 5 (Floppy disk)

Device 0 (Primary Master IDE)

Device 1 (Primary Slave IDE)

Device 2 (Secondary Master IDE)

Device 3 (Secondary Slave IDE)

```

These options are for event monitoring. The settings for each of these options are *Monitor* or *Ignore*. The Optimal default setting for all devices is *Ignore*. The Fail-Safe default setting is *Ignore* except for Device 6.

#### 2-1-5 PCI/PnP Setup

#### Plug and Play-Aware OS

The settings for this option are Yes or No. The Optimal and Fail-Safe default settings are No. Set this option to Yes if the operating system in the computer is aware of and follows the Plug and Play

specification. AMIBIOS only detects and enables PnP ISA adapter cards that are required for system boot. Currently, only Windows 95' is PnP-Aware. Set this option to *No* if the operating system (such as DOS, OS/2, Windows 3.x) does not use PnP. You must set this option correctly. Otherwise, PnP-aware adapter cards installed in the computer will not be configured properly.

#### PCI Latency Timer (PCI Clocks)

This option specifies the latency timings in PCI clocks for all PCI devices. The settings are 32, 64, 96, 128, 160, 192, 224, or 248. The Optimal and Fail-Safe default settings are 64.

#### PCI VGA Palette Snoop

The settings for this option are *Enabled* or *Disabled*. The Optimal and Fail-Safe default settings are *Disabled*. When set to *Enabled*, multiple VGA devices operating on different buses can handle data from the CPU on each set of palette registers on every video device. Bit 5 of the command register in the PCI device configuration space is the VGA Palette Snoop bit (0 is disabled). For example: if there are two VGA devices in the computer (one PCI and one ISA) and this option is disabled, data read and written by the CPU is only directed to the PCI VGA device's palette registers. If enabled, data read and written by the CPU is directed to both the PCI VGA device's palette registers and the ISA VGA palette registers. This will permit the palette registers of both devices to be identical. This option must be set to *Enabled* if any ISA adapter card installed in the system requires VGA palette snooping.

#### PCI IDE Bus Master

The settings are: Disabled or Enabled. The Optimal and Fail-Safe default settings are Disabled.

#### Offboard PCI IDE Card

This option specifies if an offboard PCI IDE controller adapter card is installed in the computer. The PCI expansion slot on the motherboard where the offboard PCI IDE controller is installed must be specified. If an offboard PCI IDE controller is used, the onboard IDE controller is automatically disabled. The settings are *Auto* (AMIBIOS automatically determines where the offboard PCI IDE controller adapter card is installed), *Slot 1*, *Slot 2*, *Slot 3*, *Slot 4*, *Slot 5* or *Slot 6*. The Optimal and Fail-Safe default settings are *Auto*.

This option forces IRQ14 and IRQ15 to a PCI slot on the PCI local bus. This is necessary to support non-compliant ISA IDE controller adapter cards. If an offboard PCI IDE controller adapter card is installed in the computer, you must also set the Offboard PCI IDE Primary IRQ and Offboard PCI IDE Secondary IRQ options.

# Offboard PCI IDE Primary IRQ Offboard PCI IDE Secondary IRQ

These options specify the PCI interrupt used by the primary (or secondary) IDE channel on the offboard PCI IDE controller. The settings are *Disabled*, *Hardwired*, *INTA*, *INTB*, *INTC*, or *INTD*. The Optimal and Fail-Safe default settings are *Disabled*.

DMA Channel 0 DMA Channel 1 DMA Channel 3 DMA Channel 5 DMA Channel 6 DMA Channel 7

These DMA channels control the data transfers between the I/O devices and the system memory. The chipset allows the BIOS to choose which channels to do the job. The settings are ISA/EISA or PnP. The Optimal and Fail-Safe default settings are PnP.

IRQ3 IRQ4 IRQ5 IRQ7 IRQ9 IRQ10 IRQ11 IRQ12 IRQ14 IRQ15

These options specify which bus the specified IRQ line is used on and allow you to reserve IRQs for legacy ISA adapter cards. If more IRQs must be removed from the pool, the end user can use these options to reserve the IRQ by assigning an ISA/EISA setting to it. Onboard I/O is configured by AMIBIOS. All IRQs used by onboard I/O are configured as PCI/PnP.

IRQ14 and 15 will not be available if the onboard PCI IDE is enabled. If all IRQs are set to ISA/EISA and IRQ14 and 15 are allocated to the onboard PCI IDE, IRQ 9 will still be available for PCI and PnP devices. This is because at least one IRQ must be available for PCI and PnP devices. The settings are ISA/EISA or PCI/PnP. The Optimal and Fail-Safe default settings are PCI/PnP.

#### Reserved Memory Size

This option specifies the size of the memory area reserved for legacy ISA adapter cards. The settings are *Disabled*, *16K*, *32K*, or *64K*. The Optimal and Fail-Safe default settings are *Disabled*.

#### Reserved Memory Address

This option specifies the beginning address (in hex) of the reserved memory area. The specified ROM memory area is reserved for use by legacy ISA adapter cards. The settings are *C0000*, *C4000*, *C8000*, *CC000*, *D0000*, *D4000*, *D8000*, or *DC000*. The Optimal and Fail-Safe default settings are *C8000*.

#### 2-1-6 Peripheral Setup

#### **OnBoard FDC**

This option enables the FDC (Floppy Drive Controller) on the motherboard. The settings are *Auto* (AMIBIOS automatically determines if the floppy controller should be enabled), *Enabled*, or *Disabled*. The Optimal and Fail-Safe default settings are *Auto*.

#### OnBoard Serial Port 1

This option specifies the base I/O port address of serial port 1. The settings are *Auto* (AMIBIOS automatically determines the correct base I/O port address), *Disabled*, *3F8h*, *2F8h*, *2E8h*, or *3E8h*. The Optimal and Fail-Safe default settings are *Auto*.

#### OnBoard Serial Port 2

This option specifies the base I/O port address of serial port 2. The settings are *Auto* (AMIBIOS automatically determines the correct base I/O port address), *Disabled*, *3F8h*, *2F8h*, *2E8h*, or *3E8h*. The Optimal and Fail-Safe default settings are *Auto*.

#### Serial Port 2 Mode

The settings are *Normal*, *Sharp-IR*, *IrDA*, or *TV Remote*. The Optimal and Fail-Safe default settings are *Normal*.

#### IR Duplex Mode

The settings are Half or Full. The Optimal and Fail-Safe default settings are N/A.

#### IR Receiver Pin

The settings are *IRRX1* or *IRRX2*. The Optimal and Fail-Safe default settings are *N/A*.

#### OnBoard Parallel Port

This option specifies the base I/O port address of the parallel port on the motherboard. The settings are *Auto* (AMIBIOS automatically determines the correct base I/O port address), *Disabled*, *378h*, *278h*, or *3BCh*. The Optimal and Fail-Safe default settings are *Auto*.

#### Parallel Port Mode

This option specifies the parallel port mode. The settings are *Normal*, *Bi-Dir*, *EPP* or *ECP*. The Optimal and Fail-Safe default settings are *ECP*. When set to *Normal*, the normal parallel port mode is used. Use *Bi-Dir* to support bidirectional transfers. Use *EPP* (Enhanced Parallel Port) to provide asymmetric bidirectional data transfer driven by the host device. Use *ECP* (Extended Capabilities Port) to achieve data transfer rates of up to 2.5Mbps. ECP uses the DMA protocol and provides symmetric bidirectional communication.

#### **EPP Version**

The settings are 1.7 or 1.9. The Optimal and Fail-Safe default settings are N/A.

#### Parallel Port DMA Channel

This option is only available if the setting of the parallel port mode option is ECP. The settings are 0, 1, 2, 3, 5, 6 or 7. The Optimal and Fail-Safe default settings are *Auto*.

#### Parallel Port IRQ

This option specifies the parallel port IRQ. The settings are *Auto*, 5 or 7. The Optimal and Fail-Safe default settings are *Auto*.

#### OnBoard IDE

This option specifies the onboard IDE controller channels to be used. The settings are *Disabled, Primary, Secondary*, or *Both*. The Optimal and Fail-Safe default settings are *Both*.

#### **OnBoard SCSI**

Enable the OnBoard SCSI feature to use the on-board SCSI on the motherboard. The settings are *Disabled* or *Enabled*. The Optimal and Fail-Safe default settings are *Enabled*.

#### Remote Power On

Microsoft's Memphis OS supports this feature which can wake-up the system from SoftOff state through devices (such as an external modem) that are connected to COM1 or COM2. The settings are *Disabled* or *Enabled*. The Optimal and Fail-Safe default settings are *Disabled*.

#### **CPU Current Temperature**

The current CPU temperature is displayed in this option.

#### **CPU Overheat Warning Temperature**

Use this option to set the CPU overheat warning temperature. The settings are  $25 \, ^{\circ}C$  through  $75 \, ^{\circ}C$  in  $1 \, ^{\circ}C$  intervals. The Optimal and Fail-Safe default settings are  $55 \, ^{\circ}C$ .

#### CPU Overheat Clock Down

The CPU internal clock will slow down to the specified frequency percentage when it is overheated. The settings are *Disabled*, 12.5%, 25%, 37.5%, 50%, 62.5%, 75% or 87.5%. The Optimal and Fail-Safe default settings are *Disabled*.

LM78 In0 (CPU 1)

LM78 In1 (CPU 2)

LM78 In2 (+3.3V)

LM78 In3 (+5V)

LM78 In4 (+12V)

LM78 In5 (-12V)

LM78 In6 (-5V)

CPU1 Fan

CPU2 Fan

Chassis Fan

The above features are for the on-board National Semiconductor's LM 78 System Hardware Monitor used for PC health monitoring. The motherboards with LM 78 have seven on-board voltage monitors for the CPU core, CPU I/O, +3.3V, +5V, -5V, +12V, and -12V, and three fan status monitors.

#### 2-2 Security Setup

# 2-2-1 Supervisor User

The system can be configured so that all users must enter a password every time the system boots or when the WINBIOS setup is executed. You can set either a Supervisor password or a User password. If you do not want to use a password, just press <Enter> when the password prompt appears.

The password check option is enabled in the Advanced Setup by choosing either *Always* or *Setup*. The password is stored in CMOS RAM. You can enter a password by typing the password on the keyboard, selecting each letter via the mouse, or selecting each letter via the pen stylus. Pen access must be customized for each specific hardware platform.

When you select Supervisor or User, AMIBIOS prompts for a password. You must set the Supervisor password before you can set the User password. Enter a 1-6 character password. The pass-

word does not appear on the screen when typed. Retype the new password as prompted and press <Enter>. Make sure you write it down. If you forget it, you must drain CMOS RAM and reconfigure.

#### 2-2-2 Anti-Virus

When this icon is selected, AMIBIOS issues a warning when any program (or virus) issues a disk format command or attempts to write to the boot sector of the hard disk drive. The settings are *Enabled* or *Disabled*. The Optimal and Fail-Safe default settings are *Disabled*.

#### 2-3 Utility Setup

#### 2-3-1 Language

The Optimal and Fail-Safe default settings for this option are *English*.

#### 2-3-2 Detect IDE

Use this icon to let the BIOS autodetect the IDE hard drive.

#### 2-4 Default Setting

Every option in WinBIOS Setup contains two default settings: a Fail-Safe default, and an Optimal default.

#### 2-4-1 Optimal Default

The Optimal default settings provide optimum performance settings for all devices and system features.

#### 2-4-2 Fail-Safe Default

The Fail-Safe default settings consist of the safest set of parameters. Use them if the system is behaving erratically. They should always work but do not provide optimal system performance characteristics.

## Appendix A Hard Disk Error Messages

The first group of errors listed below may appear during the initialization process, before anything else happens.

- No Hard Disk Installed The program could not find a hard disk drive installed on the system. This message appears if there is no hard disk on the system and you have chosen to run the Hard Disk Utility.

- FATAL ERROR Bad Hard Disk The program is not getting a response from the hard disk, or the hard disk is not repairable. Check all cable and power connections to the hard disk.

- Hard Disk Controller Failure The program is getting an error response from the reset command sent to the hard disk controller. Check to see that the controller is seated properly in the bus slot.

- C: (D:) Hard Disk Failure The hard disk drive (C or D) is not responding to commands sent to it by the program. Check power and cable connections to the hard disk.

#### NOTE

The errors listed below may appear during operation.

- Undefined Error Command Aborted An error condition has occurred which the program cannot identify.

- Address Mark Not Found The address mark (initial address) on the hard disk could not be found.

- Requested Sector Not Found The sector currently requested on the hard disk could not be found.

- Reset Failed The program issued a reset command to the hard disk, but this command did not properly reset the hard disk.

- 9. Drive Parameter Activity Failed The program has sent a reset command to the controller, followed by the drive parameters. Using the parameters sent to it, the controller is not getting a response from the hard disk drive. Check to see if the drive type selected in the 'Standard CMOS Setup' is correct for the disk drive being used.

- Bad Sector Flag Detected The program has tried to perform an operation on a sector which has been flagged (i.e., marked as "bad").

- 11. Bad ECC on Disk Read When the program attempts to write to the disk, it also calculates an ECC (Error Correction Code) value for the data being written. This ECC value is written to the drive and then read back. If the value read back is different from the one calculated, then, this error will occur.

- 12. ECC Corrected Data Error The ECC value (explained above) read from the disk is not the same value which was written to the disk; therefore, the program assumes that the data is not correct. It, then, attempts to correct the data, but the ECC value is not corrected. In this situation, this message appears.

- Controller Has Failed The program has issued a diagnostic command to the controller, which has failed; therefore, the controller has failed as well.

- 14. Seek Operation Failed The program has issued a seek command to the drive and this operation has failed. A seek operation is the act of finding a particular sector on the hard disk.

- 15. Attachment Failed to Respond No response has been received from the hard disk drive. This message appears if an operation has already begun and the hard disk does not respond, when it has responded earlier.

- 16. Drive Not Ready The program is trying to perform an operation on the hard disk drive, and it has waited beyond a preset specified time limit. This situation is known as "timeout."

- Write Fault on Selected Drive A 'Write Fault' has occurred during the write operation on the hard disk.

# Appendix B BIOS Hard Disk Drive Types

Table B-1. AMI BIOS Hard Disk Drive Types

| Type | Cylinders | Heads | Write<br>Precompensation | Landing<br>Zone | Sectors | Size   |

|------|-----------|-------|--------------------------|-----------------|---------|--------|

| 1    | 306       | 4     | 128                      | 305             | 17      | 10 MB  |

| 2    | 615       | 4     | 300                      | 615             | 17      | 20 MB  |

| 3    | 615       | 6     | 300                      | 615             | 17      | 31 MB  |

| 4    | 940       | 8     | 512                      | 940             | 17      | 62 MB  |

| 5    | 940       | 6     | 512                      | 940             | 17      | 47 MB  |

| 6    | 615       | 4     | 65535                    | 615             | 17      | 20 MB  |

| 7    | 462       | 8     | 256                      | 511             | 17      | 31 MB  |

| 8    | 733       | 5     | 65535                    | 733             | 17      | 30 MB  |

| 9    | 900       | 15    | 65535                    | 901             | 17      | 112 MB |

| 10   | 820       | 3     | 65535                    | 820             | 17      | 20 MB  |

| 11   | 855       | 5     | 65535                    | 855             | 17      | 35 MB  |

| 12   | 855       | 7     | 65535                    | 855             | 17      | 50 MB  |

| 13   | 306       | 8     | 128                      | 319             | 17      | 20 MB  |

| 14   | 733       | 7     | 65535                    | 733             | 17      | 43 MB  |

| 16   | 612       | 4     | 0                        | 663             | 17      | 20 MB  |

| 17   | 977       | 5     | 300                      | 977             | 17      | 41 MB  |

| 18   | 977       | 7     | 65535                    | 977             | 17      | 57 MB  |

| 19   | 1024      | 7     | 512                      | 1023            | 17      | 60 MB  |

| 20   | 733       | 5     | 300                      | 732             | 17      | 30 MB  |

| 21   | 733       | 7     | 300                      | 732             | 17      | 43 MB  |

| 22   | 733       | 5     | 300                      | 733             | 17      | 30 MB  |

| 23   | 306       | 4     | 0                        | 336             | 17      | 10 MB  |

| 24   | 925       | 7     | 0                        | 925             | 17      | 54 MB  |

| 25   | 925       | 9     | 65535                    | 925             | 17      | 69 MB  |

| 26   | 754       | 7     | 754                      | 754             | 17      | 44 MB  |

| 27   | 754       | 11    | 65535                    | 754             | 17      | 69 MB  |

| 28   | 699       | 7     | 256                      | 699             | 17      | 41 MB  |

| 29   | 823       | 10    | 65535                    | 823             | 17      | 68 MB  |

| 30   | 918       | 7     | 918                      | 918             | 17      | 53 MB  |

| 31   | 1024      | 11    | 65535                    | 1024            | 17      | 94 MB  |

| 32   | 1024      | 15    | 65535                    | 1024            | 17      | 128 MB |

| 33   | 1024      | 5     | 1024                     | 1024            | 17      | 43 MB  |

| 34   | 612       | 2     | 128                      | 612             | 17      | 10 MB  |

| 35   | 1024      | 9     | 65535                    | 1024            | 17      | 77 MB  |

| 36   | 1024      | 8     | 512                      | 1024            | 17      | 68 MB  |

Table B-1. AMI BIOS Hard Disk Drive Types (Continued)

| Type | Cylinders | Heads  | Write<br>Precompensation | Landing<br>Zone | Sectors | Size   |

|------|-----------|--------|--------------------------|-----------------|---------|--------|

| 37   | 615       | 8      | 128                      | 615             | 17      | 41 ME  |

| 38   | 987       | 3      | 987                      | 987             | 17      | 25 ME  |

| 39   | 987       | 7      | 987                      | 987             | 17      | 57 ME  |

| 40   | 820       | 6      | 820                      | 820             | 17      | 41 ME  |

| 41   | 977       | 5      | 977                      | 977             | 17      | 41 ME  |

| 42   | 981       | 5      | 981                      | 981             | 17      | 41 ME  |

| 43   | 830       | 7      | 512                      | 831             | 17      | 48 ME  |

| 44   | 830       | 10     | 65535                    | 830             | 17      | 69 ME  |

| 45   | 917       | 15     | 65535                    | 918             | 17      | 114 MI |

| 46   | 1224      | 15     | 65535                    | 1223            | 17      | 152 MI |

| 47   | ENTER     | RPARAM | ETERS PROVIDED WIT       | HHARDDR         | IVE     |        |

### Appendix C BIOS Error Beep Codes

During the POST (Power-On Self-Test) routines, which are performed each time the system is powered on, errors may occur.

**Non-fatal errors** are those which, in most cases, allow the system to continue the boot-up process. The error messages normally appear on the screen. See Appendix E for BIOS Error Messages.

**Fatal errors** are those which will not allow the system to continue the boot-up procedure. If a fatal error occurs, you should consult with your system manufacturer for possible repairs.

These fatal errors are usually communicated through a series of audible beeps. The numbers on the fatal error list below correspond to the number of beeps for the corresponding error. All errors listed, with the exception of #8, are fatal errors.

| Beeps | Error message                              | Description                                                                                                                                                                            |

|-------|--------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | Refresh Failure                            | The memory refresh circuitry on the motherboard is faulty.                                                                                                                             |

| 2     | Parity Error                               | A parity error was detected in the base memory (the first 64 KB block) of the system.                                                                                                  |

| 3     | Base 64 KB Memory Failure                  | A memory failure occurred within the first 64 KB of memory.                                                                                                                            |

| 4     | Timer Not Operational                      | A memory failure was detected in the first 64 KB of memory, or Timer 1 is not functioning.                                                                                             |

| 5     | Processor Error                            | The CPU on the system board generated an error.                                                                                                                                        |

| 6     | 8042 - Gate A20 Failure                    | The keyboard controller (8042) contains the Gate A20 switch which allows the CPU to operate in virtual mode. This error means that the BIOS cannot switch the CPU into protected mode. |

| 7     | Processor Exception<br>Interrupt Error     | The CPU on the motherboard generated an exception interrupt.                                                                                                                           |

| 8     | Display Memory Read/Write<br>Error         | The system video adapter is either missing or its memory is faulty.  Please Note: This is not a fatal error.                                                                           |

| 9     | ROM Checksum Error                         | The ROM checksum value does not match the value encoded in the BIOS.                                                                                                                   |

| 10    | CMOS Shutdown Register<br>Read/Write Error | The shutdown register for CMOS memory has failed.                                                                                                                                      |

| 11    | Cache memory bad -<br>do not enable cache  | The cache memory test failed. Cache memory is disabled. Do not press <ctrl>+<alt>+<shift> and &lt;+&gt; to enable cache memory.</shift></alt></ctrl>                                   |

## Appendix D

# AMI BIOS POST Diagnostic Error Messages

This section describes the power-on self-tests (POST) port 80 codes for the AMI BIOS.

| Check Point | <u>Description</u>                                                                                                                                                                      |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 03          | NMI is Disabled Checking soft reset and power-on next.                                                                                                                                  |

| 05          | Soft reset/power-on determined. Going to disable cache (i.e., disable shadow RAM/cache, if any).                                                                                        |

| 06          | Post code to be uncompressed. CPU init and CPU data area init to be done next.                                                                                                          |

| 07          | Post code is uncompressed. CPU init and CPU data area init to be done next.                                                                                                             |

| 08          | CPU and CPU data area init done. CMOS checksum calculation to be done next.                                                                                                             |

| 09          | The CMOS checksum calculation is done and the CMOS RAM diagnostic byte has been written. CMOS RAM initialization is next if the <i>Initialize CMOS RAM At Every Boot</i> option is set. |

| 0A          | CMOS RAM is initialize. The CMOS RAM status register will be initialized for Date and Time next.                                                                                        |

| ОВ          | The CMOS RAM status register has been initialized. Any initialization before the keyboard BAT test will be done next.                                                                   |

| Check Point | <u>Description</u>                                                                                                                                                                                         |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0C          | The keyboard controller I/B is free. Issuing the BAT command to the keyboard controller next.                                                                                                              |

| 0D          | The BAT command was issued to the keyboard controller. Verifying the BAT command next.                                                                                                                     |

| 0E          | The keyboard controller BAT result has been verified. Any initialization after the keyboard controller BAT command will be done next.                                                                      |

| 0F          | Initialization after the keyboard controller BAT command is done. The keyboard command byte will be written next.                                                                                          |

| 10          | The keyboard controller command byte has been written. Issuing the keyboard controller pins 23 and 24 blocking and unblocking command next.                                                                |

| 11          | Keyboard controller pins 23 and 24 have been blocked and unblocked. See if the <ins> key has been pressed during power-on next.</ins>                                                                      |

| 12          | Checked if the <ins> key was pressed during power-<br/>on. Disabling the DMA and Interrupt controllers.</ins>                                                                                              |

| 13          | DMA controllers 1 and 2 and interrupt controllers 1 and 2 have been disabled. The video display is disabled and port B is initialized. Initializing the chipset and doing automatic memory detection next. |

| 15          | Chipset initialization/auto memory detection over.<br>Next, 8254 timer test about to start.                                                                                                                |

| 19          | The 8254 timer test has completed. Starting the memory refresh test.                                                                                                                                       |

| Check Point | <u>Description</u>                                                                                                |

|-------------|-------------------------------------------------------------------------------------------------------------------|

| 1A          | Memory Refresh line has been toggled. Going to check 15 microseconds ON/OFF time.                                 |

| 20          | Memory Refresh period 30 microsecond test completed. Base 64 KB memory test and address line test about to start. |

| 23          | Base 64 KB sequential data R/W test passed. Any setup before Interrupt vector initialize about to start.          |

| 24          | Setup required before vector initialization completed. Interrupt vector initialization about to begin.            |

| 25          | Interrupt vector initialization done. Going to read I/O port of 8042 for turbo switch (if any).                   |

| 26          | Input port of 8042 is read. Going to initialize global data for turbo switch.                                     |

| 27          | Global data initialization is over. Any initialization before setting the video mode to be done next.             |

| 28          | Initialization before setting the video mode has been completed. Going for monochrome/color mode setting.         |

| 2A          | Different BUSes init (system, static, output devices) to start if present.                                        |

| 2B          | About to give control for any setup required before optional video ROM check.                                     |

| 2C          | Processing before video ROM control is done. About to look for optional video ROM and give control.               |

| Check Point | Description                                                                                                             |

|-------------|-------------------------------------------------------------------------------------------------------------------------|

| 2D          | Optional video ROM control is done. About to give control to do any processing after video ROM returns control to post. |

| 2E          | Return from processing after the video ROM control. If EGA/VGA not found, then do display memory R/W test.              |

| 2F          | EGA/VGA not found. Display memory R/W test about to begin.                                                              |

| 30          | Display memory R/W test passed. Looking for the retrace checking.                                                       |

| 31          | Display memory R/W test or retrace checking failed. About to do alternate Display memory R/W test.                      |

| 32          | Alternate Display memory R/W test passed. About to look for the alternate display retrace checking.                     |

| 34          | Video display checking over. Display mode to be set next.                                                               |

| 37          | Display mode set. Going to display the power-on message.                                                                |

| 38          | Different BUSes init (input, IPL, general devices) to start if present.                                                 |

| 39          | Display different BUSes initialization error messages.                                                                  |

| 3A          | New cursor position read and saved. Going to display the Hit <del> message next.</del>                                  |

| 3B          | "Hit <del>" message is displayed. Virtual mode memory test about to start.</del>                                        |

| 40          | Preparing the descriptor tables next.                                                                                   |

| 42          | Descriptor tables prepared. Going to enter in virtual mode for memory test.                                             |

| Check Point | Description                                                                                                                                                         |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 43          | Entered in the virtual mode. Going to enable interrupts for diagnostics mode.                                                                                       |

| 44          | Interrupts enabled (if diagnostics switch is on). Going to initialize data to check memory remap at 0:0.                                                            |

| 45          | Data initialized. Going to check for memory remap at 0:0 and find the total system memory size.                                                                     |

| 46          | Memory remap test done. Memory size calculation over. About to go for writing patterns to test memory.                                                              |

| 47          | Pattern to be tested written in extended memory. Going to write patterns in base 640 KB memory.                                                                     |

| 48          | Patterns written in base memory. Going to find out amount of memory below 1 MB memory.                                                                              |

| 49          | Amount of memory below 1 MB found and verified. Going to find out amount of memory above 1 MB memory.                                                               |

| 4B          | Amount of memory above 1 MB found and verified. Checking for soft reset and clearing the memory below 1 MB for a soft reset. (If at power on, go to checkpoint 4E). |

| 4C          | Memory below 1 MB cleared. (SOFT RESET.) Going to clear memory above it.                                                                                            |

| 4D          | Memory above 1 MB cleared. (SOFT RESET.) Going to save the memory size. Going to checkpoint 52 next.                                                                |

| 4E          | Memory test started. (NO SOFT RESET.) About to display the first 64 KB memory test.                                                                                 |

| 4F          | Memory size display started. This will be updated during memory test. Going for sequential and random memory test.                                                  |

| Check Point | <u>Description</u>                                                                                                            |

|-------------|-------------------------------------------------------------------------------------------------------------------------------|

| 50          | Memory test below 1 MB completed. Going to adjust memory size for relocation/shadow.                                          |

| 51          | Memory size adjusted due to relocation/shadow. Memory test above 1 MB to follow.                                              |

| 52          | Memory test above 1 MB completed. Saving the memory size information.                                                         |

| 53          | CPU registers are saved including memory size. Going to enter into real mode.                                                 |

| 54          | Shutdown successful, CPU in real mode. Going to disable Gate A20 address line.                                                |

| 57          | The Gate A20 address line is disabled. Adjusting the memory size depending the memory relocation and/or shadowing parameters. |

| 58          | The memory size has been adjusted for memory relocation and/or shadowing. Clearing the Hit <del> message next.</del>          |

| 59          | "Hit <del>" message cleared. "WAIT" message displayed. About to start DMA and interrupt controller test.</del>                |

| 60          | DMA page register test passed. About to verify from display memory.                                                           |

| 62          | DMA #1 base register test passed. About to go for DMA #2 base register test.                                                  |

| 65          | DMA #2 base register test passed. Programming DMA controllers 1 and 2 next.                                                   |

| 66          | DMA unit 1 and 2 programming over. About to initialize 8259 interrupt controller.                                             |

| Check Point | Description                                                                                                                 |

|-------------|-----------------------------------------------------------------------------------------------------------------------------|

| 67          | 8259 initialization over. About to start keyboard test.                                                                     |

| 7F          | Extended NMI sources enabling is in progress.                                                                               |

| 80          | Keyboard test started. Clearing output buffer, checking for stuck key. About to issue keyboard reset command.               |

| 81          | Keyboard reset error/stuck key found. About to issue keyboard controller interface test command.                            |

| 82          | Keyboard controller interface test over. About to write command byte and initialize circular buffer.                        |

| 83          | Command byte written. Global data initialization done. About to check for lock-key.                                         |

| 84          | Lock-key checking over. About to check for memory size mismatch with CMOS.                                                  |

| 85          | Memory size check done. About to display soft error and check for password or bypass setup.                                 |

| 86          | Password checked. About to do programming before setup.                                                                     |

| 87          | Programming before setup completed. Going to CMOS setup program.                                                            |

| 88          | Returned from CMOS setup program and screen is cleared. About to do programming after setup.                                |

| 89          | Programming after setup completed. Going to display power-on screen message.                                                |

| 8B          | First screen message displayed. "WAIT" message is also displayed. Shadowing of the system and video BIOS will be done next. |

| Check Point | Description                                                                                                                     |

|-------------|---------------------------------------------------------------------------------------------------------------------------------|

| 8C          | Main and Video BIOS shadow successful. Setup options programming after CMOS setup about to start.                               |

| 8D          | Setup options are programmed. The mouse check and initialization will be done next.                                             |

| 8E          | The mouse check and initialization are done. Going for hard disk reset.                                                         |

| 8F          | The hard disk reset is complete. About to go for floppy check.                                                                  |

| 91          | Floppy setup is over. Test for hard disk presence to be done.                                                                   |

| 94          | Hard disk setup completes. About to set the base and extended memory sizes.                                                     |

| 96          | Memory size adjusted due to mouse support, hard disk type-47. Going to do any initialization before C8000 optional ROM control. |

| 97          | Any initialization before C8000 optional control is over. Checking the C8000 adaptor ROM, then passing control to it next.      |

| 98          | C8000 adaptor ROM has passed control to POST. Going to do any required processing after C8000 adaptor ROM returns control next. |

| 99          | Any initialization required after optional ROM test over. Going to set up timer data area and printer base address.             |

| 9A          | Return after setting timer and printer base address.<br>Going to set the RS-232 base address.                                   |

| 9B          | Returned after RS-232 base address. Going to do any initialization before coprocessor test.                                     |

| Check Point | Description                                                                                                           |

|-------------|-----------------------------------------------------------------------------------------------------------------------|

| 9C          | Required initialization before coprocessor test is over.<br>Going to initialize the coprocessor next.                 |

| 9D          | Coprocessor initialized. Going to do any initialization after coprocessor test.                                       |

| 9E          | Initialization after coprocessor test is completed.<br>Going to check extended keyboard, keyboard ID and<br>num-lock. |

| 9F          | Extended keyboard check, ID flag set, num-lock on/off is done. Keyboard ID command to be issued.                      |

| A0          | Keyboard ID command is issued. Keyboard ID flag to be reset.                                                          |

| A1          | Keyboard ID flag reset. Cache memory test to follow.                                                                  |

| A2          | Cache memory test over. Going to display any soft errors.                                                             |

| A3          | Soft error display complete. Going to set the keyboard typematic rate.                                                |

| A4          | Keyboard typematic rate set. Going to program memory wait states.                                                     |

| A5          | Memory wait states programming over. Screen to be cleared next. Going to enable parity and NMI.                       |

| A7          | NMI and parity enabled. Going to do any initialization required before giving control to optional ROM at E0000.       |

| A8          | Initialization before E000 ROM control over. E000 ROM to get control next.                                            |

| A9          | Returned from E000 ROM control. Going to do any initialization required after E000 optional ROM control.              |

### **Check Point Description**

AA Initialization after E000 optional ROM control is over. Going to display the system configuration. В0 configuration is system displayed. Uncompressing the Setup code for hotkey setup next, if required. The setup code for hotkey has been uncompressed. В1 Copying any required code to a specific area. 00 The code has been copied to a specific area. Going

to give control to INT 19h boot loader.

## Appendix E BIOS Non-Fatal Error Messages

If a non-fatal error occurs during the POST routines performed each time the system is powered on, the error message will appear on the screen in the following format:

```

ERROR Message Line 1

ERROR Message Line 2

Press <F1> to RESUME

```

Note the error message and press the <F1 > key to continue with the boot up sequence.

#### NOTE

If the "Wait for <F1> If Any Error" option in the Advanced CMOS Setup portion of the BIOS SETUP PROGRAM has been set to "disabled," the <FI> prompt will not appear on the third line.