# **CU430HX Motherboard** Technical Product Specification

Order Number 281839-002 February 1997

The CU430HX motherboard may contain design defects or errors known as errata. Characterized errata that may cause the CU430HX motherboard's behavior to deviate from published specifications are documented in the CU430HX Motherboard Specification Update.

## **Revision History**

| Revision | Revision History                                                | Date |

|----------|-----------------------------------------------------------------|------|

| -001     | Initial release of the CU430HX Technical Product Specification. | 8/96 |

| -002     | Incorporate minor changes.                                      | 2/97 |

This product specification applies only to standard CU430HX motherboards with BIOS identifier 1.00.0X.DK0.

Changes to this specification will be published in the CU430HX Motherboard Specification Update before being incorporated into a revision of this document.

Information in this document is provided in connection with Intel products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel retains the right to make changes to specifications and product descriptions at any time, without notice.

The CU430HX motherboard may contain design defects or errors known as errata. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications before placing your product order.

<sup>†</sup> Third-party brands and names are the property of their respective owners.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature, may be obtained from:

Intel Corporation P.O. Box 7641 Mt. Prospect, IL 60056-7641

or call in North America 1-800-879-4683, Europe 44-0-1793-431-155, France 44-0-1793-421-777, Germany 44-0-1793-421-333, other Countries 708-296-9333.

Copyright © 1996, Intel Corporation

## **Table of Contents**

| 1 | Mot                                   | herboa  | rd Description7                                                 |  |

|---|---------------------------------------|---------|-----------------------------------------------------------------|--|

|   | 1.1                                   | Overvie | ew7                                                             |  |

|   | 1.2 Motherboard Manufacturing Options |         |                                                                 |  |

|   | 1.3 Form Factor                       |         |                                                                 |  |

|   | 1.4 Microprocessor                    |         |                                                                 |  |

|   |                                       | 1.4.1   | Microprocessor Upgrade11                                        |  |

|   |                                       | 1.4.2   | Main System Memory11                                            |  |

|   | 1.5                                   | Chipset | t12                                                             |  |

|   |                                       | 1.5.1   | 82439HX Xcelerated Controller (TXC)12                           |  |

|   |                                       | 1.5.2   | 82371SB PCI/ISA IDE Xcelerator (PIIX3)12                        |  |

|   |                                       | 1.5.3   | Universal Serial Bus (USB) Support13                            |  |

|   |                                       | 1.5.4   | IDE Support13                                                   |  |

|   | 1.6                                   | Super I | /O Controller (National PC87306B)13                             |  |

|   |                                       | 1.6.1   | Floppy Controller14                                             |  |

|   |                                       | 1.6.2   | Keyboard and Mouse Interface14                                  |  |

|   |                                       | 1.6.3   | Real-time Clock, CMOS RAM and Battery15                         |  |

|   |                                       | 1.6.4   | Infrared Support15                                              |  |

|   |                                       | 1.6.5   | Parallel Port15                                                 |  |

|   | 1.7                                   | ATI-GT  | 3-D Graphics Controller                                         |  |

|   |                                       | 1.7.1   | Graphics Upgrade Options16                                      |  |

|   |                                       | 1.7.2 R | esolutions Supported16                                          |  |

|   |                                       | 1.7.3   | Graphics Drivers and Utilities16                                |  |

|   | 1.8                                   | Audio S | Subsystem (Creative Labs Vibra 16C)17                           |  |

|   |                                       | 1.8.1   | Resource Map17                                                  |  |

|   |                                       | 1.8.2   | Audio Drivers                                                   |  |

|   | 1.9                                   | 0       | ement Extension Hardware18                                      |  |

|   | 1.10                                  | Onboar  | d Networking18                                                  |  |

|   |                                       | 1.10.1  | EtherExpress™ PRO/100B PCI LAN Subsystem                        |  |

|   |                                       | 1.10.2  | Intel 82557 LAN Controller19                                    |  |

|   |                                       | 1.10.3  | 10/100Mbps Physical Layer Interface19                           |  |

|   |                                       | 1.10.4  | EtherExpress PRO/100B PCI LAN Subsystem Software Description.19 |  |

|   | 1.11 | Motherl             | board Connectors               | 20 |

|---|------|---------------------|--------------------------------|----|

|   |      | 1.11.1              | Front Panel Connectors         | 21 |

|   |      | 1.11.2              | Memory/Expansion Connectors    | 24 |

|   |      | 1.11.3              | Audio Connectors               | 26 |

|   |      | 1.11.4              | Power Connectors               | 27 |

|   |      | 1.11.5              | Floppy/IDE Connectors          | 29 |

|   |      | 1.11.6              | Hardware Monitoring Connectors | 30 |

|   |      | 1.11.7              | Video Connectors               | 31 |

|   |      | 1.11.8              | USB/Serial Connectors          | 33 |

|   |      | 1.11.9              | Back Panel Connectors          | 33 |

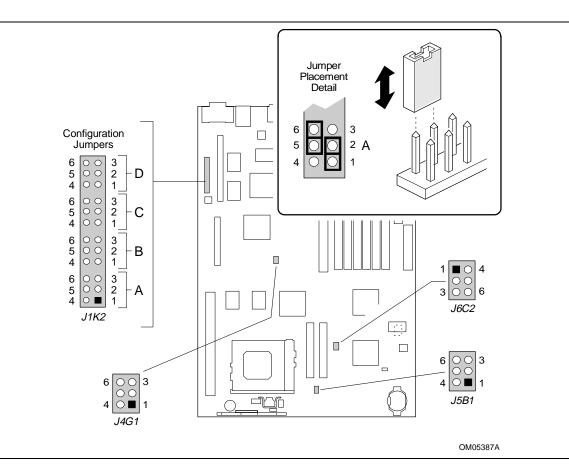

|   | 1.12 | 2 Jumper            | <sup>r</sup> Settings          | 37 |

|   | 1.13 | 8 Reliabil          | ity                            | 39 |

|   | 1.14 | Environ             | imental                        | 39 |

|   | 1.15 | o Power             | Consumption                    | 39 |

|   |      | 1.15.1              | Power Supply Considerations    | 40 |

|   | 1.16 | Regula <sup>®</sup> | tory Compliance                | 40 |

|   |      | 1.16.1              | Safety                         | 40 |

|   |      | 1.16.2              | ЕМІ                            | 41 |

|   |      | 1.16.3              | Product Certification Markings | 41 |

| 2 | Mot  | herboa              | rd Resources                   | 43 |

|   | 2.1  | Memory              | у Мар                          | 43 |

|   | 2.2  | I/O Map             | >                              | 43 |

|   | 2.3  | PCI Co              | nfiguration Space Map          | 45 |

|   | 2.4  | DMA C               | hannels                        | 46 |

|   | 2.5  | Interrup            | ots                            | 46 |

| 3 | Mot  | herboa              | rd BIOS and Setup Utility      | 47 |

| - | 3.1  |                     | ction                          |    |

|   | 3.2  |                     | lash Memory Organization       |    |

|   | 3.3  |                     | lpgrades                       |    |

|   | 3.4  |                     | E Support                      |    |

|   | 3.5  |                     | to-configuration               |    |

|   | 3.6  |                     | ig and Play                    |    |

|   | 3.7  |                     | ed Power Management            |    |

|   | 3.8  |                     | ige Support                    |    |

|   |      |                     | ан                             |    |

|   | 3.9                      | Boot Op  | otions                                   | 50 |  |  |

|---|--------------------------|----------|------------------------------------------|----|--|--|

|   | 3.10                     | Flash L0 | OGO Area                                 | 50 |  |  |

|   | 3.11 Setup Enable Jumper |          |                                          |    |  |  |

|   | 3.12                     | BIOS Se  | etup Utility                             | 51 |  |  |

|   |                          | 3.12.1   | Overview of the Setup Menu Screens       | 51 |  |  |

|   |                          | 3.12.2   | Main BIOS Setup Screen                   | 52 |  |  |

|   |                          | 3.12.3   | Floppy Options Subscreen                 | 53 |  |  |

|   |                          | 3.12.4   | Hard Disk Configuration Subscreen        | 53 |  |  |

|   |                          | 3.12.5   | Boot Options Subscreen                   | 54 |  |  |

|   |                          | 3.12.6   | Advanced Screen                          | 56 |  |  |

|   |                          | 3.12.7   | Peripheral Configuration Subscreen       | 57 |  |  |

|   |                          | 3.12.8   | Advanced Chipset Configuration Subscreen | 59 |  |  |

|   |                          | 3.12.9   | Power Management Configuration Subscreen | 59 |  |  |

|   |                          | 3.12.10  | Plug and Play Configuration Subscreen    | 60 |  |  |

|   |                          | 3.12.11  | Event Logging Configuration              | 61 |  |  |

|   |                          | 3.12.12  | Security Screen                          | 63 |  |  |

|   |                          | 3.12.13  | Security Screen Options                  | 64 |  |  |

|   |                          | 3.12.14  | Exit Screen                              | 64 |  |  |

| 4 | Erro                     | or Messa | ages and Beep Codes                      | 65 |  |  |

|   | 4.1                      |          | eep Codes                                |    |  |  |

|   | 4.2                      |          | figuration Error Messages                |    |  |  |

|   | 4.3                      |          | rror Messages                            |    |  |  |

|   | 4.4                      |          | I Messages                               |    |  |  |

|   |                          |          |                                          |    |  |  |

## **1** Motherboard Description

## 1.1 Overview

The CU430HX motherboard has been designed for use in the commercial desktop market. The CU430HX motherboard supports the following set of features:

- Uses a 9-inch by 13-inch LPX form factor.

- Uses a type 7 Zero Insertion Force (ZIF) socket to house any of the Intel Pentium<sup>®</sup> processors, and provides an upgrade path to future Pentium OverDrive<sup>®</sup> processors.

- Accepts Pentium processors with core clock frequencies of 75 MHz, 90/100 MHz, 120 MHz, 133 MHz, 150 MHz, 166 MHz, and 200 MHz.

- Uses Intel's 82430HX PCIset. The Intel 82371SB PCI/ISA IDE Xccelerator (PIIX3) provides an integrated Bus Mastering IDE controller with two high performance IDE interfaces for up to four devices (such as hard drives or CD-ROM).

- Supports up to 192 MB of DRAM using six standard 72-pin tin lead SIMM<sup>+</sup> sockets that accept Fast Page Mode (FPM) and Extended Data Out (EDO) memory. Both non-parity (32-bit wide) and parity (36-bit wide), as well as ECC memory SIMMs are supported.

- Uses a Flash BIOS with the following features:

- Uses both hardware and software Secure Flash features to protect Flash contents from corruption.

- Uses a BIOS that complies with the Desktop Management Interface (DMI-compliant).

- Uses the National PC87306BV I/O controller to integrate the following standard PC I/O functions:

- floppy interface,

- two FIFO serial ports,

- one EPP/ECP capable parallel port,

- a Real Time Clock,

- keyboard controller,

- support for an IrDA<sup>†</sup> and Consumer Infra Red compatible interface.

- Integrates an ATI<sup>†</sup> Mach64GT graphics controller with SGRAM graphics memory to support SVGA graphics at resolutions up to 1280 x 1024 with 1MB of SGRAM installed. Supports up to 4MB of graphics memory using an add-in module from ATI.

- Integrates a business audio solution using a Creative Laboratories 16C audio codec on the motherboard to provide 16-bit stereo, Sound Blaster Pro<sup>+</sup> compatible audio.

- Integrates a complete LAN interface onboard using the Intel 82557 LAN controller.

- Provides an onboard telephony (modem) connector to support the latest telephony applications.

- A hardware monitoring ASIC provides the following monitoring functions:

- Integrated temperature sensor

- Fan speed monitoring

- Power supply voltage monitoring

- Storage of POST results and error codes

- Back panel connectors are provided for video and audio, the PS/2 keyboard/mouse, a parallel interface, an RJ45 LAN interface, and the serial interface. An optional Universal Serial Bus (USB) connector provides two USB connectors instead of the single serial DB9 connector.

- PCI and ISA expansion slots are supported by a connector on the motherboard designed to accept a riser card. An on-board jumper allows support of risers with either two or three PCI slots.

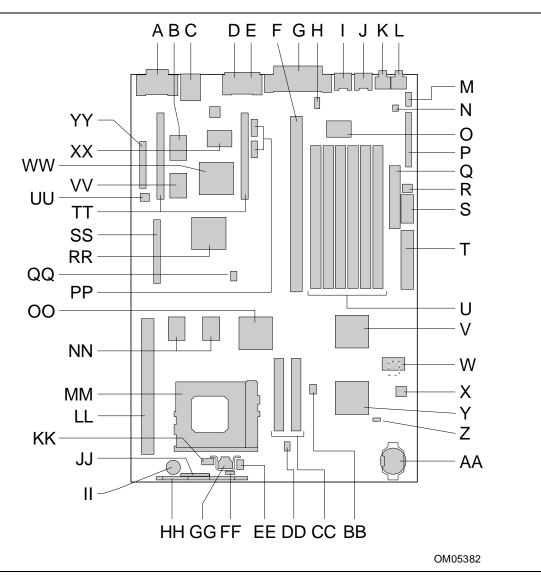

Figure 1. Motherboard Features

| Key | Description                                           | Key | Description                                     | Key | Description                                       |

|-----|-------------------------------------------------------|-----|-------------------------------------------------|-----|---------------------------------------------------|

| A   | VGA connector (15-pin,<br>J1N1)                       | В   | SGRAM, video, 128Kx32x2<br>(U2L2)               | С   | LAN connector (RJ45, J2N1)                        |

| D   | Side-by-side USB<br>connector option (4x1x2,<br>J4N1) | E   | Serial connector option (9-<br>pin, J4N2)       | F   | ISA/PCI riser socket (J6J2)                       |

| G   | Parallel connector (DB25, J6N1)                       | Н   | CD Audio header (1x4,<br>J6N2)                  | I   | PS/2 Mouse connector<br>(J7N1)                    |

| J   | PS/2 Keyboard Connector<br>(J8N1)                     | к   | Microphone input jack<br>(J8N2)                 | L   | Audio output jack (J9N2)                          |

| Μ   | Wave Table header (2x4,<br>J9N1)                      | N   | Telephony (modem)<br>header (2x2, J9M1)         | 0   | Creative Labs Vibra16C<br>audio controller (U7M1) |

| Ρ   | MIDI/Audio header<br>(2x17,J9L1)                      | Q   | Floppy connector (J9K1)                         | R   | Soft-OFF header (1x3,<br>J9K2)                    |

| S   | Std 3.3V power connector (J9J1)                       | Т   | Main power connector<br>(J9H1)                  | U   | SIMM sockets (J6J1, J7J1, J7J2, J7J3, J8J1, J8J2) |

| V   | National PC87306B Ultra<br>I/O controller (U7E1)      | W   | Flash BIOS<br>TSOP/PSOP(E28F002,<br>U9D1, U9D2) | Х   | Hardware monitor ASIC<br>(U9C1)                   |

| Y   | Intel SB82371SB (PIIX3,<br>U7C1)                      | Z   | Intrusion-detect photo-<br>transistor (Q8B1)    | AA  | Real-time clock battery<br>(BT9A1)                |

| BB  | Flash recovery jumper<br>block (2x3, J6C2)            | сс  | IDE connectors (J5C1,<br>J6C1)                  | DD  | Vcc regulator header (2x3,<br>J5B1)               |

| EE  | 3-wire fan header (1x3,<br>J4A4)                      | FF  | Keyboard lock header (1x3, J4A3)                | GG  | Voltage regulator (U3A1)                          |

| нн  | Front panel connector (1x29, J4A1)                    | П   | Onboard speaker (LS2A1)                         | JJ  | Front panel header 2 (1x9, J2A2)                  |

| KK  | PWR/HDD LED header<br>(1x4, J3A2)                     | LL  | CELP socket (J1D1)                              | MM  | Socket 7 Pentium<br>processor socket (U3C1)       |

| NN  | Mcache PBSRAM<br>(32Kx32, U3E1, U2E1)                 | 00  | Intel FW82439HX (TXC,<br>U4E1)                  | PP  | COM1/COM2 header (5x2, J4L1, J4M1)                |

| QQ  | Jumper block, 2/3 PCI slot<br>(2x3, J4G1)             | RR  | ATI 264GT-B video<br>controller (U3H1)          | SS  | VGA header (2x20, J1H1)                           |

| TT  | Video memory upgrade<br>header (2x27, J1L1, J4L2)     | UU  | Security header (1x2,<br>J1K1)                  | VV  | SGRAM, video, 128Kx32x2<br>(U2K2)                 |

| WW  | LAN Controller (82557,<br>U3K1)                       | xx  | National DP83840 (U3L1)                         | ΥY  | Jumper block header<br>(J1K2)                     |

Table 1.

Key to Motherboard Features

## **1.2 Motherboard Manufacturing Options**

Contact your local Intel Field Sales Office for options and ordering information.

## 1.3 Form Factor

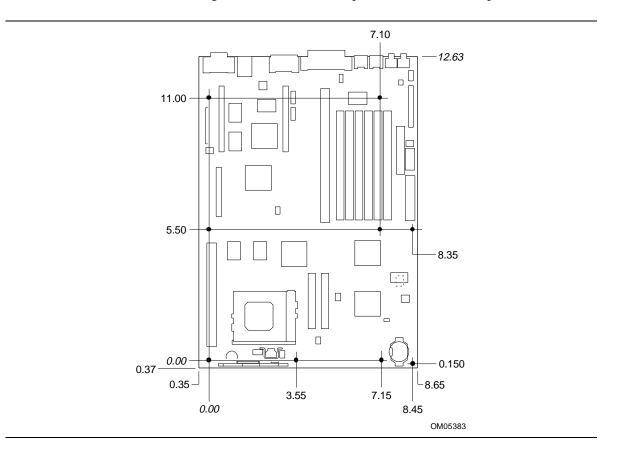

The CU430HX motherboard is designed to fit into a standard LPX form factor chassis. Figure 2 illustrates the mechanical form factor for the CU430HX motherboard. Location of the I/O connectors, riser slot, and mounting holes are in strict compliance with the LPX specification.

Figure 2. Motherboard Dimensions

## 1.4 Microprocessor

The CU430HX motherboard is designed to operate with 3.3 volt Pentium processors. An onboard linear voltage regulator circuit provides the required 3.3 volts from the 5.0 volt tap of the power supply. An on-board jumper enables use of OverDrive processors and Pentium processors with MMX<sup>™</sup> technology. All Pentium processors (those running internally at 75, 90, 100, 120, 133, 150, 166, and 200 MHz) are supported.

The Pentium processor maintains full backward compatibility with the 8086, 80286, Intel386<sup>™</sup> and Intel486<sup>™</sup> processors. It supports both read and write burst mode bus cycles, and includes separate 8 KB on-chip code and data caches that employ a write-back policy. The Pentium processor has an advanced numeric coprocessor that significantly increases the speed of floating point operations, while maintaining backward compatibility with math coprocessors that comply with ANSI/IEEE standard 754-1985.

## 1.4.1 Microprocessor Upgrade

The CU430HX motherboard provides a 321-pin Socket 7 ZIF processor socket. Socket 7 supports a processor upgrade path that includes all Pentium OverDrive processors.

## 1.4.2 Main System Memory

The board has six 72-pin, tin lead SIMM sockets, arranged as three banks, each with two sockets. Some important considerations are:

- The board supports Fast Page Mode (FPM) memory in 70ns (or faster) SIMMs, and either 70ns or 60ns Extended Data Out (EDO) SIMMs. If the maximum host bus speed is 60MHz or slower, 70ns EDO DRAM can be used.

- The board supports both parity and ECC memory.

- Both sockets of a bank must be used.

- Both sockets of a bank must contain the same type (fast page or EDO), speed (60 or 70ns), and size of SIMM.

- You can have different types, speeds, and sizes in different banks.

- Only tin lead 72-pin SIMMs can be used with the standard tin lead SIMM sockets.

- There are no jumper settings required for the memory size or type. This information is automatically detected by the system BIOS.

The sockets support the following SIMM sizes:

| SIMM Size | Configuration<br>(without parity) | Configuration (with parity) |

|-----------|-----------------------------------|-----------------------------|

| 4 MB      | 1 M x 32                          | 1 M x 36                    |

| 8 MB      | 2 M x 32                          | 2 M x 36                    |

| 16 MB     | 4 M x 32                          | 4 M x 36                    |

| 32 MB     | 8 M x 32                          | 8 M x 36                    |

## 1.5 Chipset

•

The Intel 82430HX PCIset consists of the 82439HX Xcelerated Controller (TXC) and one 82371SB PCI/ISA IDE Xcelerator (PIIX3) bridge chip.

## 1.5.1 82439HX Xcelerated Controller (TXC)

The 82439HX provides all control signals necessary to drive a second level cache and the DRAM array, including multiplexed address signals. The TXC also controls system access to memory and generates snoop controls to maintain cache coherency. The TXC comes in a 324-pin BGA package and includes the following features:

- CPU interface control

- Integrated L2 write-back cache controller

- Pipeline burst SRAM

- 256 or 512 KB direct-mapped

- Integrated DRAM controller

- 64 bit path to memory

- Support for EDO and fast page DRAM

- 8 MB to 512 MB main memory

- Parity, non-parity, and ECC memory support

- Fully synchronous PCI bus interface

- 25/30/33 MHz

- PCI to DRAM > 100 Mbytes/sec

- Up to 4 PCI masters in addition to the PIIX3 and IDE.

## 1.5.2 82371SB PCI/ISA IDE Xcelerator (PIIX3)

The PIIX3 provides the interface between the PCI and ISA buses and integrates a dual channel fast IDE interface capable of supporting up to four devices. The PIIX3 integrates seven DMA channels, one 16-bit timer/counter, two eight-channel interrupt controllers, PCI-to-AT interrupt mapping circuitry, NMI logic, ISA refresh address generation, and PCI/ISA bus arbitration circuitry together on the same device. The PIIX3 comes in a 208-pin QFP package and includes the following features.

- Interface between the PCI and ISA buses

- Universal Serial Bus controller

- Host/hub controller

- Integrated fast IDE interface

- Support for up to four devices

- PIO Mode 4 transfers up to 16 MB/sec

- Integrated 8 x 32-bit buffer for bus master PCI IDE burst transfers

- Bus master mode

- PCI 2.1 compliant

- Enhanced fast DMA controller

- Interrupt controller and steering

- Counters/timers

- SMI interrupt logic and timer with fast on/off mode

## 1.5.3 Universal Serial Bus (USB) Support

The CU430HX motherboard optionally provides two USB ports. This permits connection of two USB peripheral devices directly to the system without an external hub. If more devices are required, an external hub can be connected to either of the built-in ports. The CU430HX motherboard completely supports the standard universal host controller interface (UHCI) and takes advantage of the standard software drivers written to be compatible with UHCI. Features of the USB include:

- Support for hot swapping of Plug and Play devices without opening the system chassis.

- Both low-speed and high-speed devices can be intermixed on the bus.

- Self-identifying peripherals.

- Automatic mapping of function to driver and configuration.

- Support for isochronous and asynchronous transfer types over the same set of wires.

- Support for up to 127 physical devices.

- Guaranteed bandwidth and low latencies appropriate for telephony, audio, and other applications.

- Error handling and fault recovery mechanisms built into protocol.

- Low cost cables and connectors.

## 1.5.4 IDE Support

The motherboard provides two independent high performance bus-mastering PCI IDE interfaces capable of supporting PIO Mode 3 and Mode 4 devices. The system BIOS supports Logical Block Addressing (LBA) and Extended Cylinder Sector Head (ECHS) translation modes as well as ATAPI (e.g. CD-ROM) devices on both IDE interfaces. Detection of IDE device transfer rate and translation mode capability is automatically determined by the system BIOS.

Programmed I/O operations normally require a substantial amount of CPU bandwidth. In true multi-tasking operating systems like Windows<sup>†</sup> 95, the CPU bandwidth freed up by using bus mastering IDE can be used to complete other tasks while disk transfers are occurring. When used in conjunction with the appropriate driver for the Windows 95 environment, the IDE interface can operate as a PCI bus master capable of supporting PIO Mode 4 devices with transfer rates of up to 16 MB/sec.

## 1.6 Super I/O Controller (National PC87306B)

Control for the integrated serial ports, parallel port, floppy drive, RTC and keyboard controller is incorporated into a single component, the National Semiconductor 306BV. This component provides:

- Two NS16C550-compatible UARTs with send/receive 16 byte FIFO

- Support for an IrDA compliant Infra Red interface

- Multi-mode bi-directional parallel port

- Standard mode; IBM and Centronics compatible

- Enhanced Parallel Port (EPP) with BIOS/Driver support

- High Speed mode; Extended Capabilities Port (ECP) compatible

- Industry standard floppy controller with 16 byte data FIFO (2.88 MB floppy support)

- Integrated Real Time Clock accurate within +/- 13 minutes/yr at 25° C and 5 volts when the system is continuously powered on.

- Integrated 8042 compatible keyboard controller

By default, the 306BV interfaces are automatically configured by the BIOS during boot-up. You can also manually configure the interfaces with the BIOS Setup utility. Chapter 3 describes and tells how to invoke the BIOS Setup utility.

## 1.6.1 Floppy Controller

The I/O controller is software compatible with the DP8473 and 82077 floppy disk controllers. You can configure the floppy interface for 360 KB or 1.2 MB 5<sup>1</sup>/<sub>4</sub> inch media, or for 720 KB, 1.2 MB, 1.44 MB, or 2.88 MB 3<sup>1</sup>/<sub>2</sub> inch media with the BIOS setup utility. By default, the Floppy A interface is configured for 1.44 MB and Floppy B is disabled. A Setup option makes it possible to prevent a user from being able to write to a floppy drive. A driver is required for configuring the floppy interface for 1.2 MB 3.5-inch (3-mode floppy) operation.

### 1.6.2 Keyboard and Mouse Interface

PS/2<sup>†</sup> keyboard and mouse connectors are located on the back panel side of the motherboard. The 5V lines to these connectors are protected with a PolySwitch<sup>†</sup> circuit that acts much like a self-healing fuse, re-establishing the connection after an over-current condition is removed. While this device eliminates the possibility of having to replace a fuse, you should still be sure to turn off the system power before installing or removing a keyboard or mouse.

## ⇒ NOTE

Although they are labeled as "Keyboard" and "Mouse" on the motherboard and the back panel, the PS/2 keyboard/mouse connectors can be used interchangeably for either keyboard or mouse. The BIOS detects the attached devices during POST, and configures the system accordingly.

The integrated 8042 microcontroller contains the AMI Megakey keyboard and mouse controller code that, besides providing traditional keyboard and mouse control functions, supports Power-On/Reset (POR) password protection. The POR password can be defined by the user via the Setup program. The keyboard controller also provides for the following "hot key" sequences:

- <CTRL><ALT><DEL>: System software reset. This sequence performs a software reset of the system by jumping to the beginning of the BIOS code and running the POST operation.

- <CTRL><ALT><+> and <CTRL><ALT><->: Turbo mode selection.

- <CTRL><ALT><-> sets the system for de-turbo mode, emulating an 23 MHz AT.

- <CTRL><ALT><+> sets the system for turbo mode. Changing the Turbo mode may be prohibited by an operating system, or when the CPU is in Protected mode or virtual x86 mode under DOS.

- <CTRL><ALT><defined in setup>: Power down and coffee-break key sequences take advantage of the SMM capabilities of the Pentium processor to greatly reduce the system's power consumption while maintaining the responsiveness necessary to service external interrupts.

• <CTRL><ALT><defined in setup>: Keyboard lock key sequence provides system security by blanking the screen and ignoring keyboard input until the BIOS User Password is typed. When the Keyboard lock sequence is invoked, the keyboard LEDs will flash to indicate that the User Password must be entered to unlock the system. This feature will not take effect unless the User Password has been set in the BIOS setup.

#### 1.6.3 Real-time Clock, CMOS RAM and Battery

The integrated real-time clock (RTC) is DS1287 and MC146818 compatible and provides a time of day clock, 100-year calendar with alarm features and is accurate to within 13 minutes per year. The RTC can be set via the BIOS SETUP program. The RTC also supports 242-byte battery-backed CMOS RAM in two banks which is reserved for BIOS use. The CMOS RAM can be set to specific values or cleared to the system default values using the BIOS SETUP program. Also, the CMOS RAM values can be cleared to the system defaults by using a configuration jumper on the motherboard.

An external coin-cell style battery provides power to the RTC and CMOS memory. The battery has an estimated lifetime of three years if the system is not plugged into the wall socket. When the system is plugged in, power is supplied from the power supply 5v standby current to extend the life of the battery.

#### 1.6.4 Infrared Support

A 5-pin header connector is provided to allow connection to a Hewlett Packard HSDSL-1000 compatible Infra-red (IrDA) transmitter/receiver. Once the module is connected to the header, Serial port 2 can be re-directed to the IrDA module. Once configured for IrDA, the user can transfer files to or from portable devices such as laptops, PDA's and printers using application software such as LapLink<sup>†</sup>. The IrDA specification provides for data transfers at 115 Kbps from a distance of 1 meter.

The Consumer Ir is receive only (for the motherboard) and can be used to control telephony functions and multimedia operation such as volume control, CD track change, and related functions.

#### 1.6.5 Parallel Port

The parallel port can be configured in the BIOS setup as output only compatible mode, bidirectional mode, ECP or EPP modes. The parallel port can also be assigned to I/O addresses 278H, 378H, or 3BCH and IRQ's 5 or 7. Furthermore, a routable DMA scheme allows Plug and Play operating systems such as Windows 95 to route either DMA channels 1 or 3 to the parallel port for ECP mode. EPP BIOS support must be provided by a device driver or TSR.

## 1.7 ATI-GT 3-D Graphics Controller

The ATI-GT 3-D graphics controller is a highly integrated, 208 pin, VLSI multimedia graphics and video controller that integrates the following features:

- Controller housed in a 208-pin PQFP package.

- The controller implements video acceleration and 3-D rendering.

- The controller supports 3-D rendering with as little as 1MB of SGRAM graphic memory.

- The controller is able to become a PCI bus master.

- The controller supports connection to Plug and Play monitors with both DDC1 (Data Display Channel 1) and DDC2B capability. This allows changing of the monitor resolutions and color options without rebooting the computer.

#### 1.7.1 Graphics Upgrade Options

The CU430HX motherboard has several headers that support expansion of the graphic subsystem. The LBP VESA feature connector supports connection to devices such as ATI MPEG and TV products.

Two video memory upgrade connectors support connection to video memory upgrade modules from ATI. These upgrade modules allow upgrading the total video memory from the standard 1MB (or 2MB) of onboard SGRAM, to either 2MB or 4MB of total video memory.

#### 1.7.2 Resolutions Supported

Table 2 lists the available video resolutions using the video controller and a standard 1MB of SGRAM video memory. The controller supports 3-D rendering with as little as 1MB of SGRAM graphic memory. The video memory can be upgraded to a maximum of 4MB of video memory using plug-in daughterboards. Refer to the video controller data sheet for the video resolutions available with more than 1MB of video memory.

| Resolution               | Supported with 1 MB SGRAM | Refresh Rate (Hz) |

|--------------------------|---------------------------|-------------------|

| 640 x 480 x 256 colors   | Yes                       | 100               |

| 640 x 480 x 64K colors   | Yes                       | 100               |

| 640 x 480 x 16.7M colors | Yes                       | 100               |

| 800 x 600 x 256 colors   | Yes                       | 100               |

| 800 x 600 x 64K colors   | Yes                       | 100               |

| 800 x 600 x 16.7M colors | No                        | 100               |

| 1024 x 768 x 256 colors  | Yes                       | 100               |

| 1024 x 768 x 64K colors  | No                        | 100               |

| 1152 x 864 x 256 colors  | Yes                       | 80                |

| 1152 x 864 x 64K colors  | No                        | 80                |

| 1280 x 1024 x 16 colors  | Yes                       | 75                |

| 1280x 1024 x 256 colors  | No                        | 75                |

#### Table 2. Supported Video Resolutions

#### 1.7.3 Graphics Drivers and Utilities

Common graphics drivers and utilities for DOS, Windows 3.1x, Windows 95, and other operating systems, as well as a variety of applications (such as AutoCAD) are available for the CU430HX motherboard. Contact your vendor for a list of available drivers. The Windows 3.1x and Windows 95 drivers include the ATI WinSwitch utility that allows users to change screen resolution without rebooting Windows, and the ATI DeskTop that supports panning and scrolling across a virtual workspace of up to 2048 x 1536.

Drivers for some operating systems such as  $OS/2^{\dagger}$  are native to the operating systems. Drivers for  $SCO^{\dagger}$  and Interactive UNIX<sup>†</sup> should be obtained from the respective UNIX vendor. Although Windows 95 installs native drivers for the onboard video, these drivers are not optimized, so you should obtain and install the accelerated drivers available through your vendor.

## 1.8 Audio Subsystem (Creative Labs Vibra 16C)

The CU430HX motherboard optionally features a 16-bit stereo audio subsystem. The audio subsystem is based upon the Creative Labs Vibra 16C (CT2505) multimedia codec. The Vibra 16C provides all the digital audio and analog mixing functions required for recording and playing of audio on personal computers. The Creative Labs Vibra 16C is a single chip VLSI solution which integrates FM synthesis, is Sound Blaster compatible and Roland MPU-401 UART mode compatible. Creative Labs Vibra 16C also provides MPCII, Adlib, and Multimedia PC Level 2 compliance to meet all of the requirements of today's multi-media applications.

The Vibra 16C has been implemented as a Plug and Play motherboard device. This means that there is a device node defined for the Vibra 16C and the BIOS must configure it. Although it is not a Plug and Play device, the Vibra 16C is very flexible in that it accommodates a variety of I/O addresses, DMA channels and interrupts.

The audio subsystem requires up to two DMA channels (to support full duplex operation) and one interrupt. When the Vibra 16C is programmed for full duplex operation, two DMA channels are assigned: one of the channels will be a 16-bit channel and the other will be 8 bits. The system can be configured to use either DMA channels 1 or 3 (8 bit channels) and DMA channels 5 or 7 (16 bit channels). The interrupt can be mapped to IRQ 5, 7, 9, or 10. The base address register is also configurable for a variety of base addresses ranging from I/O address 220 through address 280 (see the resource map below for more details). The ICU (ISA Configuration Utility) must be installed and configured before installing the DOS and Windows audio drivers.

#### 1.8.1 Resource Map

Table 3 lists the interrupts, DMA channels, and I/O addresses associated with the audio subsystem of the CU430HX motherboard.

| Device                 | Interrupt (IRQ)     | DMA Channel            | I/O Address         |

|------------------------|---------------------|------------------------|---------------------|

| Creative Labs 16C Base | 2/9                 | 8 bit DMA 1 (default)  | 220h-233h (default) |

|                        | 5 (default)         | 8 bit DMA 3            | 240h-253h           |

|                        | 7                   | 16 bit DMA 5 (default) | 260h-273h           |

|                        | 10                  | 16 bit DMA 7           | 280h-293h           |

| FM Synthesis           |                     |                        | 388h-38Bh           |

| Joystick (midi-port)   |                     |                        | 200h-207h           |

| MPU-401                | default is disabled |                        | 300h-301h           |

|                        |                     |                        | 330h-331h           |

Table 3. Vibra 16C Resource Map

## 1.8.2 Audio Drivers

Audio software and utilities are provided on the foundation software CD for the CU430HX motherboard for DOS, Windows 3.1x, and Windows 95. A setup program installs the appropriate software programs and utilities onto the system hard drive. Included in the audio software are DOS utilities that allow the user to play a CD-ROM, control sound volume and mixer settings, run diagnostics, and switch between Sound Blaster Pro and Windows Sound System modes. Windows drivers and utilities include the Windows sound driver, audio input control panel, audio mixer control panel, and a business audio transport utility.

## 1.9 Management Extension Hardware

The Management Extension hardware option provides low-cost instrumentation capabilities designed to reduce the total cost of PC ownership. The Management Extension hardware incorporates features that support the requirements of the Desktop Management Interface (DMI) compliant areas of the BIOS, as well as those of the LANDesk<sup>®</sup> Client Manager software. The hardware implementation is a single-chip ASIC with the following features:

- An integrated temperature sensor plus support for an external temperature sensor

- Support for a fan speed sensor

- Power supply voltage monitoring to detect levels above or below acceptable values

- Registers for storing power on self test (POST) hardware test results and error codes

- Intrusion detection support for an onboard photo-transistor and an optional mechanical switch. Allows detection of physical intrusion, such as when the chassis lid has been removed (even when power is off)

- Remote reset capabilities from a remote peer or server through LANDesk Client Manager, Version 3.0 and service layers (when available)

- Hardware compatibility with Windows NT<sup>†</sup>.

When an out-of-range condition (temperature, fan speed, or voltage) is reached, an interrupt is activated. The Management Extension circuitry connects to the ISA bus as an 8-bit I/O mapped device and uses the I/O addresses identified in the I/O map.

## 1.10 Onboard Networking

## 1.10.1 EtherExpress<sup>™</sup> PRO/100B PCI LAN Subsystem

The EtherExpress<sup>™</sup> PRO/100B PCI LAN Subsystem is an high performance Ethernet LAN subsystem that provides both 10Base-T and 100Base-TX connectivity. Features include:

- 32 bit direct bus mastering on the PCI bus.

- Shared memory structure in the host memory that copies data directly to/from host memory.

- 10Base-T and 100Base-TX capability using a single RJ-45 connector.

- IEEE 802.3u Auto-Negotiation for hardware selection of highest operating speed.

- Support for boot ROM (Flash or EPROM) up to 256 KB.

- Jumperless configuration; the LAN subsystem is totally software configurable.

## 1.10.2 Intel 82557 LAN Controller

This device is the heart of the LAN subsystem and provides the following functions:

- CSMA/CD Protocol Engine

- Compatible with the PCI Bus Interface 2.1

- DMA engine for movement of commands, status, and network data across PCI

- Access to EEPROM

- Standard MII interface for access to IEEE 802.3u compliant physical layer devices

## 1.10.3 10/100Mbps Physical Layer Interface

The physical layer interface is implemented in two devices from National Semiconductor, the DP83840 and the DP83223 (a.k.a. the "Twister"). The DP83840 provides:

- Complete functionality necessary for the 10Base-T interface; directly drives the cable when in 10Mbps mode.

- All functionality required for the 100Base-TX interface except for the NRZ to MLT3 encoding/decoding function, which is provided by the DP83223 "Twister" device.

- Complete set of MII management registers for control and status reporting.

- 802.3u Auto-Negotiation for automatically establishing the best possible operating mode when connected to other 10Base-T or 100Base-TX devices, whether half or full-duplex capable.

## 1.10.4 EtherExpress PRO/100B PCI LAN Subsystem Software Description

The software provided with the EtherExpress PRO/100B PCI LAN subsystem includes setup/diagnostic software (SETUP.EXE) and a readme file viewer (README.EXE) that lists supported drivers.

## 1.11 Motherboard Connectors

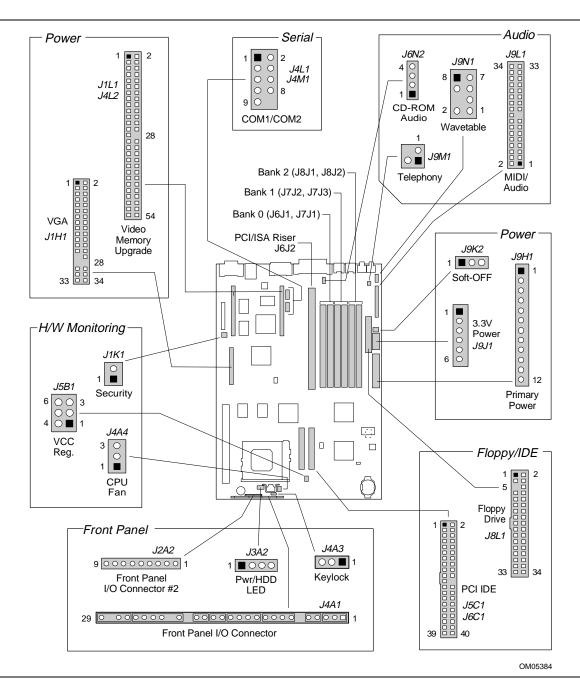

Figure 3 shows the location and functions of the motherboard connectors and headers.

Figure 3. Motherboard Connector Locations

#### 1.11.1 Front Panel Connectors

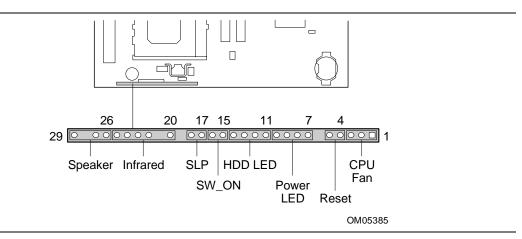

The motherboard provides header connectors to support functions typically located on the chassis bezel. Figure 4 shows the front panel connector header. Front panel features supported include:

- CPU fan (FAN)

- System Reset (RST)

- Power LED (PWRLED)

- Hard drive activity LED (HDDLED)

- Power supply ON (PS-ON)

- Sleep/Resume (SLP)

- Infrared (IrDA) port (IR)

- System Speaker (SPKR)

Figure 4. Front Panel I/O Connectors

Table 4 lists the pinouts and signals for the front panel I/O connector.

| Pin | Signal Name   | Pin | Signal Name   |  |

|-----|---------------|-----|---------------|--|

| 1   | FANNEG        | 16  | Ground        |  |

| 2   | FANPOS        | 17  | SLEEP         |  |

| 3   | FANNEG        | 18  | SLEEPPU       |  |

| 4   | Ground        | 19  | No connection |  |

| 5   | SW_RST        | 20  | VCC           |  |

| 6   | No connection | 21  | No connection |  |

| 7   | PWR_PU        | 22  | IRRIN         |  |

| 8   | PWR_PU        | 23  | Ground        |  |

| 9   | PWR_LED_DRV   | 24  | IRTX          |  |

| 10  | PWR_LED_DRV   | 25  | CONIR         |  |

| 11  | HDD_PU        | 26  | SPKR+         |  |

| 12  | HDA#          | 27  | SPKRHDR       |  |

| 13  | PWR_LED_DRV   | 28  | No connection |  |

| 14  | PWR_PU        | 29  | Ground        |  |

| 15  | SW_ON         |     |               |  |

Table 4.

Front Panel I/O Connector (J2A1)

## 1.11.1.1 CPU Fan (FAN)

The 3-pin fan header of the front panel connector provides a basic 3-wire connection to a CPU fan. The center pin of the header supplies +12 VDC and the outer pins are at ground.

#### 1.11.1.2 System Reset (RST)

This 2-pin header can be connected to a momentary SPST type switch that is normally open. When the switch is closed, the system will hard reset and run POST.

#### 1.11.1.3 Power LED (PWRLED)

This 4-pin header drives an LED to indicate when power is applied to the motherboard.

#### 1.11.1.4 Hard Drive Activity LED (HDDLED)

This 4-pin header drives an LED to indicate when hard drive activity is taking place.

#### 1.11.1.5 Power Supply ON (PS-ON)

This 2-pin header connects to a front panel power switch. When the switch is closed, the power supply turns ON. If a mechanical switch is connected to this header, it must apply a momentary ground to the SW\_ON header pin in order to signal the supply to turn ON or OFF. Because of the motherboard's internal debounce circuitry, the ground must be applied for at least 50ms. At least 2 seconds must pass before the power supply will recognize another ON/OFF signal (to prevent "double clicking").

#### 1.11.1.6 Sleep/Resume (SLP)

When Advanced Power Management (APM) is activated in the system BIOS and the Operating System's APM driver is loaded, Sleep mode (Stand-By) can be entered in one of three ways: an optional front panel "Sleep/Resume" button, a user defined keyboard hot key, or prolonged system inactivity. The Sleep/Resume button is supported by a 2-pin header located on the front panel I/O connector. Closing the "Sleep" switch will generate an SMI (System Management Interrupt) to the processor which immediately goes into System Management Mode (SMM), the so called "Sleep" mode.

The front panel "Sleep mode" switch must be a momentary two pin SPST type that is normally open. The function of the Sleep/Resume button can also be achieved via a keyboard hot-key sequence, or by a time-out of the system inactivity timer. Both the keyboard hot-key and the inactivity timer are programmable in the BIOS setup (timer is set to 10 minutes by default). To reactivate the system, or "Resume", the user must simply press the sleep/resume button again, or use the keyboard or mouse. Mouse activity will only "wake up" the system if a mouse driver is loaded. While the system is in Stand-By or "sleep" mode it is fully capable of responding to and servicing external interrupts (such as in-coming FAX) even though the monitor will only turn on if a user interrupt (keyboard/mouse) occurs as mentioned above

#### 1.11.1.7 Infrared (IrDA<sup>†</sup>) Connector (IR)

Serial port 2 can be configured to support an IrDA module via a 6-pin header connector. Once configured for IrDA, the user can transfer files to or from portable devices such as laptops, PDA's and printers using application software such as LapLink. The IrDA specification provides for data transfers at 115 Kbps from a distance of 1 meter.

#### 1.11.1.8 Speaker (SPKR)

The CU430HX motherboard has an onboard speaker to provide basic level beep code information. The front panel speaker connection allows an external (chassis mounted) speaker to be connected. The external or the onboard speaker provides error beep code information during the Power-On Self Test, if the system cannot use the video interface. When an external (chassis mounted) speaker is connected to the 2-pin header on the front panel connector, the onboard speaker is disabled.

### 1.11.1.9 Other Front Panel Connectors

In addition to the front panel I/O connector, there are three other headers included in the front panel group. Two headers (front panel header #2 and pwr/HDD LED header) provide duplicate signals to those available on the front panel I/O connector. The following tables list the pinouts and signals on the remaining front panel connectors.

Table 5.

Power/HDD LED Header (J3A2)

| Pin | Signal Name |

|-----|-------------|

| 1   | HDD_PU      |

| 2   | HDA#        |

| 3   | PWR_LED_DRV |

| 4   | PWR_PU      |

| Table 0. | TOTIL Patter Header #2 (JZAZ) |

|----------|-------------------------------|

| Pin      | Signal Name                   |

| 1        | HDD_PU                        |

| 2        | HDA#                          |

| 3        | Ground                        |

| 4        | SW_RST                        |

| 5        | VCC                           |

| 6        | IRRIN                         |

| 7        | Ground                        |

| 8        | IRTX                          |

| 9        | No connection                 |

Table 6.Front Panel Header #2 (J2A2)

| Table 7. | Keylock Header | (J4A3) |

|----------|----------------|--------|

|----------|----------------|--------|

| Pin | Signal Name |  |

|-----|-------------|--|

| 1   | Ground      |  |

| 2   | KBLOCK#     |  |

| 3   | Ground      |  |

#### 1.11.2 Memory/Expansion Connectors

The CU430HX motherboard provides six 72-pin SIMM sockets for main memory. These sockets accept standard SIMM 72-pin modules, as long as they satisfy the requirements described in the "Main System Memory" section of this specification, starting on page 11.

The CU430HX motherboard uses a PCI/ISA riser connector (J6J2) to provide for expansion PCI or ISA boards. The associated riser board can support either two or three PCI slots. A pair of jumpers on the CU430HX motherboard must be set to define the number of PCI slots on the riser board. Refer to Figure 6 on page 37 for jumper block details. Table 8 contains the pinout listing for the PCI/ISA riser connector.

| Pin | Signal Name |

|-----|-------------|-----|-------------|-----|-------------|-----|-------------|

| A1  | IOCHK#      | B1  | GND         | E1  | GND         | F1  | GND         |

| A2  | SD7         | B2  | RSTDRV      | E2  | GND         | F2  | GND         |

| A3  | SD6         | B3  | Vcc         | E3  | PCIINT1#    | F3  | PCIINT3#    |

| A4  | SD5         | B4  | IRQ9        | E4  | PCIIINT2#   | F4  | PCIINT4#    |

| A5  | SD4         | B5  | -5 V        | E5  | Vcc         | F5  | Vcc         |

| A6  | SD3         | B6  | DRQ2        | E6  | Key         | F6  | Кеу         |

| A7  | SD2         | B7  | -12 V       | E7  | Vcc         | F7  | Vcc         |

| A8  | SD1         | B8  | 0WS#        | E8  | PCIRST#     | F8  | PCKLF       |

| A9  | SD0         | B9  | +12 V       | E9  | GNT0#       | F9  | GND         |

| A10 | IOCHRDY     | B10 | GND         | E10 | REQ0#       | F10 | GNT1#       |

| A11 | AEN         | B11 | SMEMW#      | E11 | GND         | F11 | GND         |

| A12 | SA19        | B12 | SMEMR#      | E12 | PCKLE       | F12 | REQ1#       |

| A13 | SA18        | B13 | IOW#        | E13 | GND         | F13 | AD31        |

| A14 | SA17        | B14 | IOR#        | E14 | AD30        | F14 | AD29        |

| A15 | SA16        | B15 | DACK3#      | E15 | 3.3 V       | F15 | 3.3 V       |

| A16 | SA15        | B16 | DRQ3        | E16 | Key         | F16 | Key         |

| A17 | SA14        | B17 | DACK1#      | E17 | 3.3 V       | F17 | 3.3 V       |

| A18 | SA13        | B18 | DRQ1        | E18 | AD28        | F18 | AD27        |

| A19 | SA12        | B19 | REFRESH#    | E19 | AD26        | F19 | AD25        |

| A20 | SA11        | B20 | SYSCLK      | E20 | AD24        | F20 | CBE3#       |

| A21 | SA10        | B21 | IRQ7        | E21 | AD22        | F21 | AD23        |

| A22 | SA9         | B22 | IRQ6        | E22 | AD20        | F22 | AD21        |

| A23 | SA8         | B23 | IRQ5        | E23 | AD18        | F23 | AD19        |

| A24 | SA7         | B24 | IRQ4        | E24 | 3.3 V       | F24 | 3.3 V       |

| A25 | SA6         | B25 | IRQ3        | E25 | Key         | F25 | Key         |

| A26 | SA5         | B26 | DACK2#      | E26 | 3.3 V       | F26 | 3.3 V       |

| A27 | SA4         | B27 | TC          | E27 | AD16        | F27 | AD17        |

| A28 | SA3         | B28 | BALE        | E28 | FRAME#      | F28 | IRDY#       |

| A29 | SA2         | B29 | Vcc         | E29 | CBE2#       | F29 | DEVSEL#     |

| A30 | SA1         | B30 | OSC         | E30 | TRDY#       | F30 | PLOCK#      |

| A31 | SA0         | B31 | GND         | E31 | STOP#       | F31 | PERR#       |

| C1  | SBHE#       | D1  | MEMCS16#    | G1  | SDONE       | H1  | SERR#       |

| C2  | LA23        | D2  | IOCS16#     | G2  | SBO#        | H2  | AD15        |

| C3  | LA22        | D3  | IRQ10       | G3  | CBE1#       | H3  | AD14        |

| C4  | LA21        | D4  | IRQ11       | G4  | PAR         | H4  | AD12        |

| C5  | LA20        | D5  | IRQ12       | G5  | GND         | H5  | GND         |

| C6  | LA19        | D6  | IRQ15       | G6  | Key         | H6  | Key         |

Table 8.

PCI/ISA Riser Connector (J6J2)

continued 🕗

| Pin | Signal Name | Pin | Signal Name | Pin | Signal Name    | Pin | Signal Name         |

|-----|-------------|-----|-------------|-----|----------------|-----|---------------------|

| C7  | LA18        | D7  | IRQ14       | G7  | GND            | H7  | GND                 |

| C8  | LA17        | D8  | DACK0#      | G8  | AD13           | H8  | AD10                |

| C9  | MEMR#       | D9  | DRQ0        | G9  | AD11           | H9  | AD8                 |

| C10 | MEMW#       | D10 | DACK5#      | G10 | AD9            | H10 | AD7                 |

| C11 | SD8         | D11 | DRQ5        | G11 | CBE0#          | H11 | AD5                 |

| C12 | SD9         | D12 | DACK6#      | G12 | AD6            | H12 | AD3                 |

| C13 | SD10        | D13 | DRQ6        | G13 | AD4            | H13 | AD1                 |

| C14 | SD11        | D14 | DACK7#      | G14 | AD2            | H14 | AD0                 |

| C15 | SD12        | D15 | DRQ7        | G15 | Key            | H15 | Key                 |

| C16 | SD13        | D16 | Vcc         | G16 | Vcc            | H16 | Vcc                 |

| C17 | SD14        | D17 | MASTER#     | G17 | GNT2           | H17 | Vcc                 |

| C18 | SD15        | D18 | GND         | G18 | (GND   REQ2) * | H18 | (GND  <br>PCCLK2) * |

|     |             |     |             | G19 | GND            | H19 | GND                 |

Table 8. PCI/ISA Riser Connector (J6J2) (continued)

\* These signals are (2 slot | 3 slot) jumpered signal names.

## 1.11.3 Audio Connectors

The pinouts and signal listings for the audio headers/connectors are provided in the following tables.

| 6N2) |

|------|

| 6N2) |

| Pin | Signal Name |

|-----|-------------|

| 1   | Ground      |

| 2   | CD-Left     |

| 3   | Ground      |

| 4   | CD-Right    |

| Table 10. | wavetable Header (J9N1) |  |  |

|-----------|-------------------------|--|--|

| Pin       | Signal Name             |  |  |

| 1         | Wave Right              |  |  |

| 2         | Ground                  |  |  |

| 3         | Wave Left               |  |  |

| 4         | Ground                  |  |  |

| 5         | Кеу                     |  |  |

| 6         | Ground                  |  |  |

| 7         | NC                      |  |  |

| 8         | MIDI_Out                |  |  |

#### Table 10. Wavetable Header (J9N1)

| Pin | Signal Name |  |

|-----|-------------|--|

| 1   | Ground      |  |

| 2   | Mono Out    |  |

| 3   | Mic In      |  |

| 4   | Кеу         |  |

#### Table 11. Telephony Header (J9M1)

#### Table 12. MIDI/Audio Upgrade Header (J9L1)

| Pin | Signal Name      | Pin | Signal Name      |

|-----|------------------|-----|------------------|

| 1   | +5 V             | 2   | +5 V             |

| 3   | Joystick Button0 | 4   | Joystick Button2 |

| 5   | Joystick X1      | 6   | Joystick X2      |

| 7   | Ground           | 8   | MIDI Out         |

| 9   | Ground           | 10  | Joystick Y2      |

| 11  | Joystick Y1      | 12  | Joystick Button3 |

| 13  | Joystick Button1 | 14  | MIDI In          |

| 15  | +5 V             | 16  | Кеу              |

| 17  | Кеу              | 18  | Кеу              |

| 19  | Line Out Right   | 20  | Ground           |

| 21  | Right Speaker    | 22  | Ground           |

| 23  | Left Speaker     | 24  | Кеу              |

| 25  | Line Out Left    | 26  | Ground           |

| 27  | Line In Right    | 28  | -12 V            |

| 29  | Line In Left     | 30  | Ground           |

| 31  | Mic In           | 32  | +12 V            |

| 33  | Ground           | 34  | Ground           |

#### 1.11.4 Power Connectors

The CU430HX motherboard must be used with a power supply that supports remote power on/off, so the motherboard can turn off the system power under software control. The Powerman utility supplied for Windows 3.1x allows for soft-off as does the shutdown icon in Windows 95 Start menu. The system BIOS turns the system power off when it receives the proper APM command from the OS. For example, Windows 95 issues this APM command after the user selects "Shutdown the computer" option. APM must be enabled in the system BIOS and OS in order for the soft-off feature to work correctly. The user has the ability to determine the state of the power supply, so if the system was turned on when power was disconnected, the system turns back on when power is reapplied or it remains off, depending on the user setup configuration in CMOS.

Table 13 provides the pinout listing for the primary power supply connector of the CU430HX motherboard.

| Pin    | Signal Name/Function |  |  |  |

|--------|----------------------|--|--|--|

| 1      | PWRGD (Power good)   |  |  |  |

| 2      | +5 V (VCC)           |  |  |  |

| 3      | +12 V                |  |  |  |

| 4, key | -12 V                |  |  |  |

| 5      | Ground               |  |  |  |

| 6      | Ground               |  |  |  |

| 7, key | Ground               |  |  |  |

| 8      | Ground               |  |  |  |

| 9      | -5 V                 |  |  |  |

| 10     | +5 V (VCC)           |  |  |  |

| 11     | +5 V (VCC)           |  |  |  |

| 12     | +5 V (VCC)           |  |  |  |

Table 13.Primary Power Supply Connector (J9H1)

Table 14 provides the pinout listing for the external 3.3 volt power supply connector of the CU430HX motherboard.

| Pin    | Name   |

|--------|--------|

| 1      | Ground |

| 2, key | Ground |

| 3      | Ground |

| 4      | +3.3 V |

| 5      | +3.3 V |

| 6      | +3.3 V |

Table 14.

External 3.3 V Power Supply Connector (J9J1)

The pinout listing for the soft-OFF power supply connector of the CU430HX motherboard is shown in Table 15. This 3-pin keyed position supports a software-controlled power supply shutoff (Soft-OFF). When connected to this position, the power supply follows remote ON/OFF commands.

Table 15.Soft-Off Power Supply Connector (J9K2)

| Pin | Signal Name/Function      |  |

|-----|---------------------------|--|

| 1   | +5 VSB (+5 Volts Standby) |  |

| 2   | PS_ON (Remote On/Off)     |  |

| 3   | PS_COM (Supply presence)  |  |

## 1.11.5 Floppy/IDE Connectors

Table 16 lists the pinout and signal names for the floppy drive connector.

| Pin | Signal Name | Pin | Signal Name      |

|-----|-------------|-----|------------------|

| 1   | Ground      | 2   | DENSEL           |

| 3   | Ground      | 4   | Reserved         |

| 5   | Кеу         | 6   | FDEDIN           |

| 7   | Ground      | 8   | Index#           |

| 9   | Ground      | 10  | Motor Enable A#  |

| 11  | Ground      | 12  | Drive Select B#  |

| 13  | Ground      | 14  | Drive Select A#  |

| 15  | Ground      | 16  | Motor Enable B#  |

| 17  | MSEN1       | 18  | DIR#             |

| 19  | Ground      | 20  | STEP#            |

| 21  | Ground      | 22  | Write Data#      |

| 23  | Ground      | 24  | Write Gate#      |

| 25  | Ground      | 26  | Track 00#        |

| 27  | MSEN0       | 28  | Write Protect#   |

| 29  | Ground      | 30  | Read Data#       |

| 31  | Ground      | 32  | Side 1 Select#   |

| 33  | Ground      | 34  | Diskette Change# |

Table 16.

Floppy Drive Connector (J9K1)

Table 17 lists the pinout and signal names for the IDE connectors.

| Table 17. | IDE Connectors | (J5C1, J6C1) |

|-----------|----------------|--------------|

|-----------|----------------|--------------|

| Pin | Signal Name   | Pin                  | Signal Name     |  |

|-----|---------------|----------------------|-----------------|--|

| 1   | Reset IDE     | 2                    | Ground          |  |

| 3   | Host Data 7   | 4                    | Host Data 8     |  |

| 5   | Host Data 6   | 6                    | Host Data 9     |  |

| 7   | Host Data 5   | ata 5 8 Host Data 10 |                 |  |

| 9   | Host Data 4   | 10                   | 10 Host Data 11 |  |

| 11  | Host Data 3   | 12                   | Host Data 12    |  |

| 13  | Host Data 2   | 14                   | Host Data 13    |  |

| 15  | Host Data 1   | 16                   | Host Data 14    |  |

| 17  | Host Data 0   | 18                   | Host Data 15    |  |

| 19  | Ground        | 20                   | Кеу             |  |

| 21  | DDRQ0 (DDRQ1) | 22                   | Ground          |  |

| 23  | I/O Write#    | 24                   | Ground          |  |

| 25  | I/O Read#     | 26                   | Ground          |  |

continued 🕗

| Pin | Signal Name          | Pin | Signal Name          |

|-----|----------------------|-----|----------------------|

| 7   | IOCHRDY              | 28  | Vcc pull-down        |

| 29  | DDACK0 (DDACK1)#     | 30  | Ground               |

| 81  | IRQ14 (IRQ15)        | 32  | Reserved             |

| 33  | DAG1                 | 34  | Reserved             |

| 5   | DAG0                 | 36  | DAG2                 |

| 7   | Chip Select 1P (1S)# | 38  | Chip Select 3P (3S)# |

| 39  | Activity#            | 40  | Ground               |

Table 17. IDE Connectors (J5C1, J6C1) (continued)

## 1.11.6 Hardware Monitoring Connectors

The hardware monitoring connectors identified in Figure 3 are all associated with the functions performed by the hardware monitoring ASIC component on the CU430HX motherboard. The following tables list the pinouts and signals of the hardware monitoring connectors.

The security connector can be connected to a chassis-mounted micro-switch that closes if the chassis cover is removed. This switch can be used in addition to the onboard photo-transistor to keep track of each time the system chassis is opened.

| Table 18. | Security Connector (J1 | K1) |

|-----------|------------------------|-----|

|-----------|------------------------|-----|

| Pin | Signal Name/Function        |  |  |  |  |

|-----|-----------------------------|--|--|--|--|

| 1   | Ground                      |  |  |  |  |

| 2   | BATPWRSLP (Battery voltage) |  |  |  |  |

#### Table 19. Vcc Regulator Header (J5B1)

| Pin | Signal Name/Function            |

|-----|---------------------------------|

| 1   | VCC3 (Output of U3A1 regulator) |

| 2   | VCC3 (Output of U3A1 regulator) |

| 3   | VCC3 (Output of U3A1 regulator) |

| 4   | VCC2                            |

| 5   | VCC2                            |

| 6   | VCC2                            |

The separate fan connector (not part of the front panel I/O connector) listed in Table 20 has a fan sense (tachometer) line so the hardware monitoring ASIC can monitor the fan speed. This connector is keyed to prevent potential fan damage.

| Pin | Signal Name/Function           |

|-----|--------------------------------|

| 1   | Ground                         |

| 2   | FANPOS (+12VDC)                |

| 3   | FAN1_SENSE (Tachometer signal) |

Table 20. CPU Fan Connector (J4A4)

#### 1.11.7 Video Connectors

The video features identified in Figure 3 are the LBP VESA connector and the video memory upgrade headers. A video memory daughtercard can be added using the video memory upgrade headers. The total installed onboard video memory can be 1MB or 2MB. With an installed video memory daughtercard, the total video memory can be either 2MB or 4MB.

Table 21 provides the pinout and signal listing for the LBP VESA feature connector.

| Pin | Signal Name / Function      | Pin | Signal Name / Function |  |

|-----|-----------------------------|-----|------------------------|--|

| 1   | Ground                      | 2   | Pixel Data 0           |  |

| 3   | Ground                      | 4   | Pixel Data 1           |  |

| 5   | Ground                      | 6   | Pixel Data 2           |  |

| 7   | Enable External Pixel Data  | 8   | Pixel Data 3           |  |

| 9   | Enable External Sync        | 10  | Pixel Data 4           |  |

| 11  | Enable External Pixel Clock | 12  | Pixel Data 5           |  |

| 13  | N/C, not used               | 14  | Pixel Data 6           |  |

| 15  | Ground                      | 16  | Pixel Data 7           |  |

| 17  | Ground                      | 18  | PCLK, Pixel Clock      |  |

| 19  | Ground                      | 20  | BLANKING               |  |

| 21  | Ground                      | 22  | HSYNC, Horizontal Sync |  |

| 23  | N/C, not used               | 24  | VSYNC, Vertical Sync   |  |

| 25  | Key (no pin)                | 26  | Ground                 |  |

| 27  | Key (no pin)                | 28  | Key (no pin)           |  |

| 29  | IICCLK                      | 30  | Ground                 |  |

| 31  | IICDAT                      | 32  | N/C                    |  |

| 33  | EN1                         | 34  | EN2                    |  |

Table 21. LBP VESA Feature Connector (J1H1)

Table 22 and Table 23 provide the pinout and signal listings for the video memory upgrade headers.

| Pin | Signal Name / Function | Pin | Signal Name / Function | Pin | Signal Name / Function |

|-----|------------------------|-----|------------------------|-----|------------------------|

| 1   | MCLK                   | 19  | VMD2                   | 37  | VMD41                  |

| 2   | Ground                 | 20  | VMD1                   | 38  | VMD42                  |

| 3   | VCC3                   | 21  | VMD0                   | 39  | VMD43                  |

| 4   | VWEVTR#                | 22  | Ground                 | 40  | VMD44                  |

| 5   | VMD8                   | 23  | VCC3                   | 41  | VMD45                  |

| 6   | VMD9                   | 24  | VCAS0R#                | 42  | Ground                 |

| 7   | VMD10                  | 25  | VCAS1R#                | 43  | VMD46                  |

| 8   | VMD11                  | 26  | VCAS2R#                | 44  | VMD47                  |

| 9   | VMD12                  | 27  | VCAS3R#                | 45  | VMD39                  |

| 10  | VMD13                  | 28  | Vacant, Key            | 46  | VMD38                  |

| 11  | VMD14                  | 29  | VCAS4R#                | 47  | VMD37                  |

| 12  | Ground                 | 30  | VCAS5R#                | 48  | VMD36                  |

| 13  | VMD15                  | 31  | VCAS6R#                | 49  | VMD35                  |

| 14  | VMD7                   | 32  | Ground                 | 50  | VMD34                  |

| 15  | VMD6                   | 33  | VCAS7R#                | 51  | VMD33                  |

| 16  | VMD5                   | 34  | VWE_CAS0R#             | 52  | Ground                 |

| 17  | VMD4                   | 35  | VWE_CAS1R#             | 53  | VCC3                   |

| 18  | VMD3                   | 36  | VMD40                  | 54  | VMD32                  |

Table 22.

Video Memory Upgrade Header #1 (J4L2)

#### Table 23. Video Memory Upgrade Header #2 (J1L1)

| Pin | Signal Name / Function | Pin | Signal Name / Function | Pin | Signal Name / Function |

|-----|------------------------|-----|------------------------|-----|------------------------|

| 1   | Ground                 | 19  | VMD31                  | 37  | VMD49                  |

| 2   | VMD16                  | 20  | VRAS0R#                | 38  | VMD50                  |

| 3   | VMD17                  | 21  | Ground                 | 39  | VMD51                  |

| 4   | VCC3                   | 22  | VRAS1R#                | 40  | VMD52                  |

| 5   | VMD18                  | 23  | VMAR0                  | 41  | Ground                 |

| 6   | VMD19                  | 24  | VMAR1                  | 42  | VMD53                  |

| 7   | VMD20                  | 25  | VMAR2                  | 43  | VMD54                  |

| 8   | VMD21                  | 26  | VMAR3                  | 44  | VMD55                  |

| 9   | VMD22                  | 27  | VMAR4                  | 45  | VMD56                  |

| 10  | VMD23                  | 28  | Vacant, Key            | 46  | VMD57                  |

| 11  | Ground                 | 29  | VMAR5                  | 47  | VMD58                  |

| 12  | VMD24                  | 30  | VCC3                   | 48  | VMD59                  |

| 13  | VMD25                  | 31  | Ground                 | 49  | VMD60                  |

| 14  | VMD26                  | 32  | VMAR6                  | 50  | VMD61                  |

| 15  | VMD27                  | 33  | VMAR7                  | 51  | DSF                    |

| 16  | VMD28                  | 34  | VMAR8                  | 52  | VMD62                  |

| 17  | VMD29                  | 35  | VMAR9                  | 53  | VMD63                  |

| 18  | VMD30                  | 36  | VMD48                  | 54  | VCC3                   |

#### 1.11.8 USB/Serial Connectors

One of the manufacturing options for the CU430HX motherboard allows substitution of a side-byside USB connector in place of the serial connector on the back panel. When the USB option is implemented, connection to the serial ports must be made using the COM1/COM2 headers (J4L1, J4M1) on the motherboard. Table 24 lists the signals and pinout for the COM1/COM2 headers, and Table 25 lists the signals and pinout for the side-by-side USB connector.

| Pin | Signal Name | Description         |  |  |

|-----|-------------|---------------------|--|--|

| 1   | DCD         | Carrier Detect      |  |  |

| 2   | DSR         | Data Set Ready      |  |  |

| 3   | SIN#        | Serial Data In      |  |  |

| 4   | RTS         | Request To Send     |  |  |

| 5   | SOUT#       | Serial Data Out     |  |  |

| 6   | CTS         | Clear To Send       |  |  |

| 7   | DTR         | Data Terminal Ready |  |  |

| 8   | RI          | Ring Indicator      |  |  |

| 9   | GND         | Chassis Ground      |  |  |

| 10  | Key         | Vacant              |  |  |

Table 24. Serial Port Headers (J4L1, J4M1)

| Table 25. | USB Port Connector (J4N1) Pinout |

|-----------|----------------------------------|

|-----------|----------------------------------|

| Pin | Signal Name |

|-----|-------------|

| 1   | Power       |

| 2   | USBP0#      |

| 3   | USBP0       |

| 4   | Ground      |

| 5   | Power       |

| 6   | USBP1#      |

| 7   | USBP1       |

| 8   | Ground      |

#### 1.11.9 Back Panel Connectors

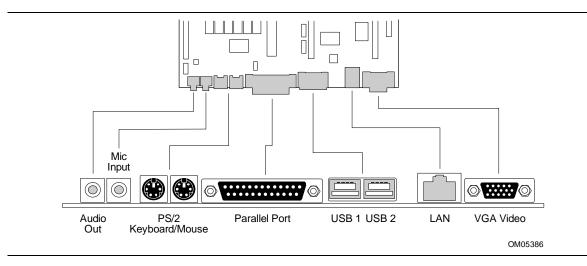

The back panel provides external access to two PS/2 style keyboard and mouse connectors, one parallel port, the microphone input and audio output connectors, an RS45 LAN connector, and a VGA video connector which are integrated on the motherboard. In addition, an RS232 serial connector or a side-by-side pair of USB connectors are also integrated on the motherboard. Figure 5 shows the general location of the I/O connectors.

Figure 5. I/O Connections

### 1.11.9.1 VGA Video Connector

Table 26 lists the pinout and signal names for the VGA video connector.

| Table 26. | VGA Video | Connector | (J1N1) |

|-----------|-----------|-----------|--------|

|-----------|-----------|-----------|--------|

| Pin | Signal Name / Function                | Pin                               | Signal Name / Function      |  |

|-----|---------------------------------------|-----------------------------------|-----------------------------|--|

| 1   | Red Video 9 Key (no pin)              |                                   | Key (no pin)                |  |

| 2   | Green Video                           | 10                                | Sync Return (Ground)        |  |

| 3   | Blue Video                            | 11                                | Monitor ID Bit 0 (not used) |  |

| 4   | Monitor ID Bit 2 (not used)           | ed) 12 Monitor ID Bit 1 (not used |                             |  |

| 5   | Chassis Ground                        | 13                                | Horizontal Sync             |  |

| 6   | Red Return (Ground)                   | 14                                | Vertical Sync               |  |

| 7   | Green Return (Ground)                 | 15                                | Not used                    |  |

| 8   | Blue Return (Ground) Shield Chassis G |                                   | Chassis Ground              |  |

## 1.11.9.2 LAN Connector

Table 27 lists the pinout and signal names for the RJ45 LAN connector.

| Table 27. | LAN Connector (J2N1) |

|-----------|----------------------|

| Pin       | Signal Name          |

| 1         | RJ45_TOP             |

| 2         | RJ45_TXM             |

| 3         | RJ45_RXP             |

| 4         | BS_TERM              |

| 5         | BS_TERM              |

| 6         | RJ45_RXM             |

| 7         | BS_TERM              |

| 8         | BS_TERM              |

#### Table 27. LAN Connector (J2N1)

#### 1.11.9.3 Serial Port Back Panel Connector

Table 28 lists the pinout and signal names for the optional serial connector.

| Signal Name | Description                                                            |  |  |

|-------------|------------------------------------------------------------------------|--|--|

| DCD         | Carrier Detect                                                         |  |  |

| SIN#        | Serial Data In                                                         |  |  |

| SOUT#       | Serial Data Out                                                        |  |  |

| DTR         | Data Terminal Ready                                                    |  |  |

| GND         | Chassis Ground                                                         |  |  |

| DSR         | Data Set Ready                                                         |  |  |

| RTS         | Request To Send                                                        |  |  |

| CTS         | Clear To Send                                                          |  |  |

| RI          | Ring Indicator                                                         |  |  |

|             | Signal Name<br>DCD<br>SIN#<br>SOUT#<br>DTR<br>GND<br>DSR<br>RTS<br>CTS |  |  |

Table 28. Serial Port Connector Pinout

#### 1.11.9.4 USB Back Panel Connectors

Table 29 lists the pinout and signal names for the USB back panel connectors.

Table 29.USB Connector Pinout

| Pin | Signal Name     |

|-----|-----------------|

| 1   | Power           |

| 2   | USBP0# [USBP1#] |

| 3   | USBP0 [USBP1]   |

| 4   | Ground          |

### 1.11.9.5 Keyboard and Mouse Ports

Table 30 lists the pinout and signal names for the PS/2 keyboard and mouse connectors. Although they are labeled as "Keyboard" and "Mouse" on the motherboard and the back panel, the connectors can be used interchangeably for either keyboard or mouse.

Table 30.

PS/2 Keyboard/Mouse Connector Pinout

| Pin    | Signal Name / Function  |

|--------|-------------------------|

| 1      | KBD/Mouse Data          |

| 2      | Reserved, No connection |

| 3      | GND, Chassis Ground     |

| 4      | +5 VDC (fused)          |

| 5      | KBD Clock               |

| 6      | Reserved, No connection |

| Shield | Chassis Ground          |

#### 1.11.9.6 Parallel Port

Table 31 lists the pinout and signal names for the parallel port connector.

| Pin | Signal Name | Description | Pin | Signal Name | Description          |

|-----|-------------|-------------|-----|-------------|----------------------|

| 1   | STB#        | Strobe      | 14  | AFD#        | Auto Feed            |