# Chapter 1 Introduction

**The 5BVPXA** mainboard is a high performance system hardware based on Intel Pentium® processor and is equipped with four PCI slots, three standard ISA slots, Super Multi-I/O controller and dual port PCI-IDE connectors for the future expansion. The hardware dimension is 220mm x 210mm with a four-layer-design technology.

#### **Specification**

- VIA Apollo VPX PCIset chipset.

- Intel Pentium Processor, AMD K5/K6 & Cyrix 6x86/6x86L/6x86MX operating at 75 ~ 333 MHz and P55C with 321 ZIF socket 7 and scalability to accept faster Processors in the future.

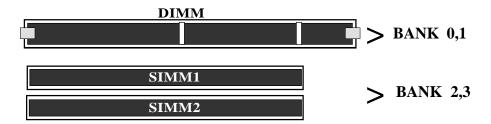

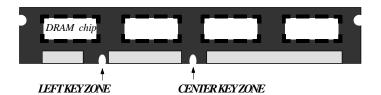

- Supports up to 192 MegaBytes of DRAM (a minimum of 8 MB) on board (72-pin SIMM x 2 & 168-pin DIMM x 1). BIOS will autometically detect and configure FP/EDO and Synchronous DRAM (Refer to Chapter 2-3 System Memory Configuration).

- Supports 512KB Onboard Pipelined Burst (synchronous) L2 Write Back/ Through Cache.

- Supports three 16 bit ISA slots and four 32 bit PCI slots and provides two independent high performance PCI IDE interfaces capable of supporting PIO Mode 3/4 and Ultra-DMA33 devices. The 5BVPXA supports four PCI Bus Masters and a jumperless PCI INT# control scheme which reduces configuration confusion when plugging in PCI I/O controller card(s).

- Supports **ATAPI** (e.g. **CD-ROM**) devices on both IDE interfaces.

- Supports 1 floppy port, 1 parallel port (EPP,ECP port), 2 serial ports (16550 Fast UART compatible) and 1 USB Connector.

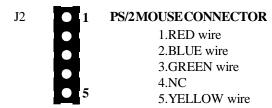

- Supports a PS/2 style mouse and standard AT style keyboard connectors.

- Supports Award Plug & Play BIOS. The BIOS is stored in Flash EPROM form. It provides better upgradeability for the system.

- Supports CPU Hardware sleep and SMM (System Management Mode).

- 5BVPXA utilizes Lithium battery which provides environmental protection and longer battery life.

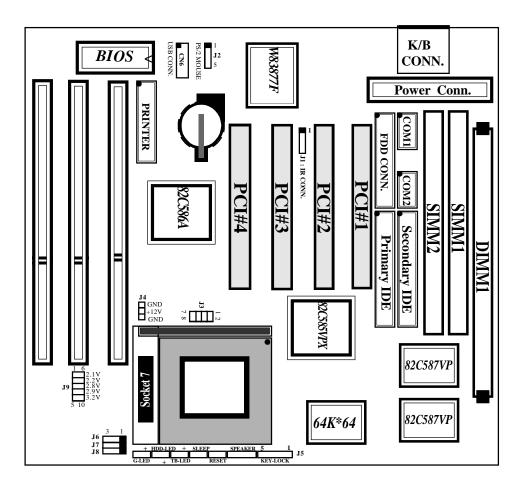

# **5BVPXA Layout**

Figure 1-1

# Chapter 2 Hardware design

#### 2-1 Mainboard Layout

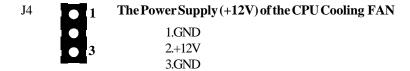

The 5BVPXA is designed with VIA Apollo VPX PCIset chipset which is developed by VIA Corporation to fully support Pentium Processor PCI/ISA system. The VIA Apollo VPX PCIset chipset can increase integration and improve performance designs. The chipset provides an integrated IDE controller with two high performance IDE interfaces for up to four IDE devices (hard devices, CD-ROM device, etc). The Winbond W83877F Super I/O controller provides the standard PC I/O function: floppy interface, two 16 Byte FIFO serial ports and EPP/ECP capable parallel port. The 5BVPXA layout is shown in the previous page for user's reference. Care must be taken when inserting memory modules, inserting CPU or even plugging PCI card into associated slots to avoid damaging any circuits or sockets on board. A cooling fan is strongly recommended when installing Pentium/Pentium MMX/K5/K6/6x86/6x86L/MX processor due to possible overheat.

**The 5BVPXA** supports a minimum of 8MB and a maximum of 192MB of System Memory while L2 Cache is 512KB synchronous SRAM Onboard to increase system performance. (Refer to **Page 2-6 Cache Memory Configuration** for the details.)

**The 5BVPXA** supports standard Fast Page, EDO (Extended Data Out or Hyper Page Mode) or synchronous DRAM. **The 5BVPXA** provides two 72-pin SIMM and one 168-pin DIMM sites for memory expansion. The sockets support 1M x 32(4MB), 2M x 32(8MB), 4M x 32(16MB), and 8M x 32(32MB) single-sided or double-sided memory modules. The memory timing requires 70 ns Fast page devices or 60 ns EDO DRAM. (DRAM Modules may be parity [x 36] or non-parity [x 32].

**The 5BVPXA** supports **two Onboard PCI IDE** connectors, and automatically detects IDE harddisk type by BIOS utility automatic.

**The 5BVPXA** supports Award Plug & Play BIOS for the ISA and PCI cards. The BIOS can be located in Flash EPROM which can replace BIOS code easily if necessary.

#### 2-2 Connectors and Jumpers

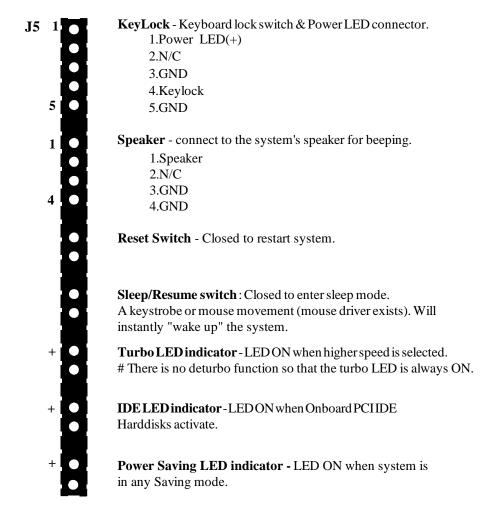

This section describes all connectors and jumpers equipped in the mainboard. Please refer to <u>Figure 1-1</u> for location of each connector and jumper.

| J1 | 1          | IrDA/ASKIR CONNECTOR |

|----|------------|----------------------|

|    |            | 1.VCC                |

|    | H          | 2.NC                 |

|    |            | 3.IRRX               |

|    |            | 4.GND                |

|    | <b>O</b> 5 | 5.IRTX               |

| J3 8      | 5 3 1  |

|-----------|--------|

|           | 3 1 _  |

| <b>J6</b> | 000    |

| <b>J7</b> |        |

| <b>J8</b> | •00    |

|           | @<br>@ |

@ @

| Intel Pentium <sup>®</sup> | Processor / | Pentium®         | MMX P | rocessor |

|----------------------------|-------------|------------------|-------|----------|

| 1                          | AMD K5/K    | <b>6</b> Install | ation | _        |

| Clock/CPU Op.              | J3          | <b>J</b> 6       | J7    | J8       |

| 60/90 MHz                  | 3-4, 5-6    | 1-2              | 1-2   | 1-2      |

| 66/100 MHz                 | 1-2, 5-6    | 1-2              | 1-2   | 1-2      |

| 60/120 MHz                 | 3-4, 5-6    | 2-3              | 1-2   | 1-2      |

| 66/133 MHz                 | 1-2, 5-6    | 2-3              | 1-2   | 1-2      |

| 60/150 MHz                 | 3-4, 5-6    | 2-3              | 2-3   | 1-2      |

| 66/166 MHz                 | 1-2, 5-6    | 2-3              | 2-3   | 1-2      |

| 66/200MHz                  | 1-2, 5-6    | 1-2              | 2-3   | 1-2      |

| 66/233MHz                  | 1-2, 5-6    | 1-2              | 1-2   | 1-2      |

| 66/266MHz                  | 1-2, 5-6    | 2-3              | 1-2   | 2-3      |

| 66/300MHz                  | 1-2, 5-6    | 2-3              | 2-3   | 2-3      |

| 66/333MHz                  | 1-2, 5-6    | 1-2              | 2-3   | 2-3      |

| Cyrix & IBM 6x86/6x86L/6x86MX Installation |             |          |            |     |     |

|--------------------------------------------|-------------|----------|------------|-----|-----|

| CPU                                        | Clock Op.   | J3       | <b>J</b> 6 | J7  | Ј8  |

| 6x86/L-PR150+                              | 60MHz * 2   | 3-4, 5-6 |            |     |     |

| 6x86/L-PR166+                              | 66MHz * 2   | 1-2, 5-6 | 2-3        | 1-2 | 1-2 |

| 6x86/L-PR200+                              | 75MHz * 2   | 3-4, 7-8 |            |     |     |

| 6x86MX-PR166                               | 66MHz * 2   | 1-2, 5-6 | 2-3        | 1-2 | 1-2 |

| 6x86MX-PR200                               | 75MHz * 2   | 3-4, 7-8 | 2-3        | 1-2 | 1-2 |

| 6x86MX-PR166                               | 60MHz * 2.5 | 3-4, 5-6 |            |     |     |

| 6x86MX-PR200                               | 66MHz * 2.5 | 1-2, 5-6 | 2-3        | 2-3 | 1-2 |

| 6x86MX-PR233                               | 75MHz * 2.5 | 3-4, 7-8 |            |     |     |

| 6x86MX-PR233                               | 66MHz * 3   | 1-2, 5-6 | 1-2        | 2-3 | 1-2 |

| 6x86MX-PR266                               | 75MHz * 3   | 3-4, 7-8 | 1-2        | 2-3 | 1-2 |

| 6x86MX-PR266                               | 66MHz * 3.5 | 1-2, 5-6 | 1-2        | 1-2 | 1-2 |

|   | idt C6 Processor Installation |           |          |            |     |     |

|---|-------------------------------|-----------|----------|------------|-----|-----|

|   | CPU                           | Clock Op. | J3       | <b>J</b> 6 | J7  | J8  |

|   | C6-DS120                      | 60MHz * 2 | 3-4, 5-6 | 2-3        | 1-2 | 1-2 |

|   | C6-DS133                      | 66MHz * 2 | 1-2, 5-6 | 2-3        | 1-2 | 1-2 |

|   | C6-DS180                      | 60MHz * 3 | 3-4, 5-6 | 1-2        | 2-3 | 1-2 |

|   | C6-DS200                      | 66MHz * 3 | 1-2, 5-6 | 1-4        | 2-3 | 1-2 |

| @ | C6-DS240                      | 60MHz * 4 | 3-4, 5-6 | 2-3        | 1-2 | 2-3 |

| @ | C6-DS266                      | 66MHz * 4 | 1-2, 5-6 | 2-3        | 1-4 | 2-3 |

| @ | C6-DS300                      | 60MHz * 5 | 3-4, 5-6 | 1-2        | 2-3 | 2-3 |

| @ | C6-DS333                      | 66MHz * 5 | 1-2, 5-6 |            |     |     |

<sup>©</sup>These jumper settings are reserved for the future CPU versions. When the future CPU versions are ready and suitable for this mainboard, these jumper settings will be correctly updated.

### J9 CPU Vcore voltage selection

0000510

1-6 : 2.1V Reserved

2-7 : 2.2V Reserved for AMD K6 in the future

3-8 : 2.8V For Intel Pentium MMX & Cyrix 6x86L

4-9 : 2.9V For AMD K6/PR2-166/200 & Cyrix 6x86MX

5-10: 3.2V For AMD K6/PR2-233/266

Note: J9 is for Vcore Settings of dual voltage CPUs. Please ignore the settings of single voltage CPUs. Such as Intel Pentium Processor, AMDK5, Cyrix MI and idt C6 here.

# 2-3 System Memory Configuration

**The 5BVPXA** supports different type of settings for the system memory. The following figures and table provides all possible memory combinations. (Please refer to **Appendix C: Memory Configuration Table** for the details).

| DIMM 1 | SIMM 1,2                               | TOTAL             |

|--------|----------------------------------------|-------------------|

| BANK 0 | BANK1                                  | Memory            |

| SDRAM  | EDO/FP DRAM  4MB — 8MB 16MB x 2 32MB — | MAX. = 192MB<br>= |

**NOTE:** 1. 5BVPXA supports both Fast Page DRAM and EDO DRAM SIMMs, but they cannot be used in the same memory bank.

$2.\,The\,KEY\,ZOOM\,of\,the\,DIMM\,socket\,is\,3.3V\,/\,Unbuffered.$

#### 2-4 Integrated PCI Bridge

The **5BVPXA** utilizes **PCIset** chipset to support Intel Pentium Processor PCI/ISA system. The VIA Apollo VPX PCIset chipset consists of the 82C585VPX system controller (TSC), two 82C587VP Data Path (TDP) devices, and one 82C586A PCI ISA/IDE Accelerator bridge chip. It provides an interface which translates CPU cycle into PCI bus cycle, and PCI burst read/write capability. In addition, it provides high performance PCI arbitor to support four PCI Masters, Rotating Priority Mechanism, and Hidden Arbitration Scheme Minimizes Arbitration Overhead.

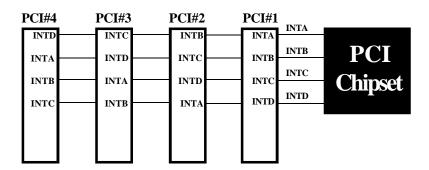

There are four interrupts in each PCI slot: INTA#, INTB#, INTC#, and INTD#. Since the **5BVPXA** adapts the PCI auto-configuration with the system BIOS Setup utility. When the system is turned on after adding a PCI add-in card, the BIOS automatically configure interrupts, DMA channels, I/O space, and other paramaters. You do not have to configure jumpers or worry about potential resource conflicts. Because PCI cards use the same interrupt resource as ISA cards, you must specify the interrupt used by ISA add-in cards in the BIOS Setup utility.

However, if a "Legacy card" (such as plugging a paddle card and cable into an ISA slot) is plugged in the system, modification in the **ROM SETUPUTILITY** becomes necessary. First of all, you must enter **PCI CONFIGURATION SETUP** utility from the **ROM SETUPUTILITY** main menu to set "ISA" for the "**PCI IDE IRQ MAPTO**

Secondly, you must enter the CHIPSET FEATURES SETUP UTILITY from the ROM SETUP UTILITY main menu and set "Disable" for the "Onboard Primary PCI IDE and the Onboard Secondary PCI IDE. When you plug PCI/ISA IDE cards into the system, You should select "Disabled" for the Onboard Primary and Secondary PCI IDE from the CHIPSET FEATURES SETUP UTILITY too.

You can set the system interrupt request (IRQ) on some "Legacy cards" which have on paddle card and cable. (refer to user's manual of the card) to a proper system IRQ level (In general, card's Primary is assigned to INTA and Secondary is assigned to INTB). If the card is plugged into slot 1(marked PCI#1), you cannot use second slot (marked PCI#2) because the Secondary INT signal takes INTB from the slot (refer to Page 3-12 for circuit diagram). The user then enters the **PCICONFIGURATION**SETUPutility from the **ROMSETUPUTILITY** main menu and set "PCI-Slot1" for the "PCI IDE IRQ MAP TO (This depends on the slot # where the Legacy card is plugged).

# CHAPTER 3 AWARD BIOS SETUP

Award's ROM BIOS provides a built-in setup program which allows user to modify the basic system configuration and hardware parameters. The modified data will be stored in a battery-backed CMOS RAM so data will be retained even when the power is turned off. In general, the information saved in the CMOS RAM stays unchanged unless there is a configuration change in the system, such as a hard drive replacement or a new device installation.

If this does happen you will need to reconfigure your configuration parameter.

## To Enter Setup Propgram

Power on the computer and press **Del**> key immediately. This will bring you into BIOS **CMOSSETUPUTILITY**.

#### ROMPCI/ISA BIOS(2A5LDPA9) **CMOSSETUPUTILITY** AWARD SOFTWARE, INC. STANDARD CMOS SETUP SUPERVISOR PASSWORD **BIOS FEATURES SETUP** USER PASSWORD CHIPSET FEATURES SETUP IDE HDD AUTO DETECTION POWER MANAGEMENT SETUP HDD LOW LEVEL FORMAT PNP/PCI CONFIGURATION SAVE & EXIT SETUP INTEGRATED PERIPHERALS EXIT WITHOUT SAVING LOAD SETUP DEFAULTS $\uparrow \quad \downarrow \longrightarrow \longrightarrow$ : SELECT ITEM ESC: QUIT F10 : Save & Exit Setup (Shift)F2: Change Color Time, Date, Hard Disk Type...

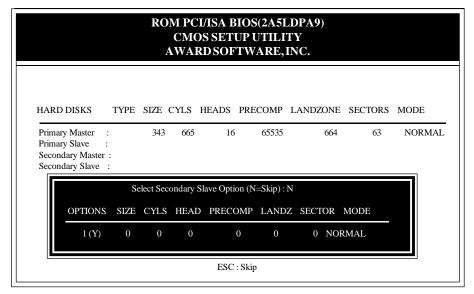

#### Figure 3-1 CMOS SETUP UTILITY

The menu displays all major selection items. Select the item you need to reconfigure. The selection is made by moving cursor (press any direction key ) to the item and press the 'Enter' key. An on-line help message is displayed at the bottom of the screen as the cursor is moving to various items which provides a better understanding of each function. When a selection is made, the menu of selected item will appear so the user can modify the associated configuration parameters.

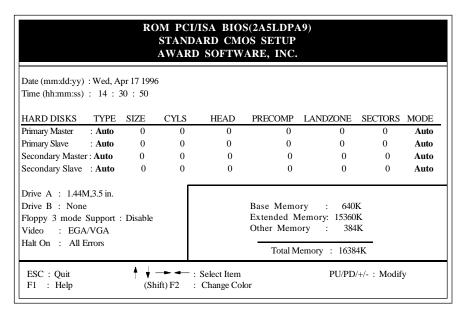

#### 3-1 STANDARD CMOS SETUP

Choose 'STANDARD CMOS SETUP' in the CMOS SETUP UTILITY Menu (Fig.3-1). The STANDARD CMOS SETUP allows user to configure system setting such as the current date and time, type of hard disk drive installed, floppy drive type, and display type. Memory size is auto-detected by the BIOS and displayed for your reference. When a field is highlighted (use direction keys to move cursor and <Enter> key to select), the entries in the field will be changed by pressing <PgDn> or <PgUp> keys or user can enter new data directly from the keyboard.

Figure 3-2 STANDARD CMOS SETUP

NOTE: If the hard disk Primary Master/Slave and the Secondary Master/Slave are set as "Auto", then the hard disk size and model will be auto-detected.

**NOTE:** The "**Halt On:**" field is to determine when to halt the system by the BIOS if an error occurrs.

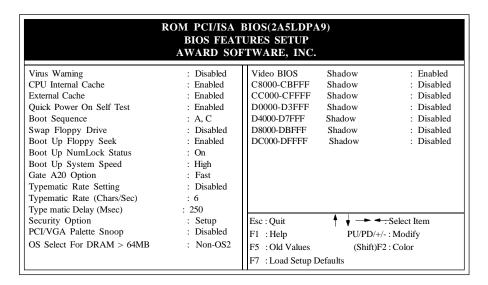

#### 3-2 BIOS FEATURES SETUP

Selecting the "BIOS FEATURES SETUP" option in the CMOS SETUP UTILITY menu allows user to change system related parameters in the displayed menu. This menu shows all of the manufacturer's default values of the 5BVPXA. Again, user can move the cursor by pressing direction keys and <PgDn> or <PgUp> keys to modify the parameters. Pressing [F1] key to display help message of the selected item.

This setup program also provides 2 convenient ways to load the default parameter data from BIOS[F6] or CMOS[F7] area if shown data is corrupted. This provides the system a capability to recover from any possible error.

Figure 3-3 BIOS FEATURES SETUP

**Note**: The **Security Option** contians "**setup**" and "**system**". The "**setup**" indicates that the password setting is for CMOS only while the "**system**" indicates the password setting is for both CMOS and system boot up.

• Virus Warning: This category flashes on the screen. During and after the system boots up, any attempt to write to the boot sector or partition table of the hard disk drive will halt the system and an error message will appear. You should then run an anti-virus program to locate the virus. Keep in mind that this feature protects only the boot sector, not the entire hard drive. Default value is Disabled.

**Enabled**: Activates automatically when the system boots up causing a warning message to appear when any attempt to access the boot sector or hard disk partition table.

**Disabled**: No warning message to appear when any attempt to access the boot sector or hard disk partition table.

• CPU Internal Cache / External Cache: These two categories speed up memory access. However, it depends on CPU/chipset design. The default value is Enabled. If your CPU is without Internal Cache then this item "CPU Internal Cache" will not be shown.

Enabled: Enable cache.Disable: Disable cache.

Quick Power On Self Test: This category speeds up Power On Self Test (POST)

after you power on the computer. If it is set to Enable, BIOS will shorten or skip

some checking items during POST.

**Enabled**: Enable quick POST.

Disabled: Normal POST.

• **Boot Sequence:** This category determines which drive is searched first for the O/S(Operating System). The default value is A,C.

**A,C**: The system will search for floppy disk drive first then hard disk drive.

**CA**: The system will search for hard disk drive first then floppy disk drive.

• **Swap Floppy Drive:** This will swap your physical drive letters A&B if you are using two floppy disks. The default value is Disabled.

**Enabled**: Floppy A & B will be swapped under the O/S.

**Disabled**: Floppy A & B will be not swapped.

• Boot Up Floppy Seek: During Power-On-Self-Test (POST), BIOS will determine if the floppy disk drive installed is 40 or 80 tracks. Only 360K type is 40 tracks while 760K, 1.2M and 1.44M are all 80 tracks. The default value is Enabled.

**Enabled**: BIOS searches for floppy disk drive to determine if it is 40 or 80 tracks. Note that BIOS cannot tell from 720K, 1.2M or 1.44M drive type as they are

all80tracks.

**Disabled**: BIOS will not search for the type of floppy disk drive by track number. Note that there will not be any warning message if the drive installed is 360K.

• Boot Up NumLock Status: The default value is On.

**On:** Keypad is number keys.

*Off*: Keypad is arrow keys.

Boot UP System Speed: Select default system speed. The system will run at the selected speed after the system boots.

**High**: Set the speed to high.

**Low**: Set the speed to low.

Gate A20 Option: This refers to the way the system addresses memory above 1MB (extended memory). The default value is Fast.

*Normal*: The A20 signal is controlled by keyboard controller or chipset hardware.

Fast: The A20 signal is controlled by Port 92 or chipset specific method.

• Typematic Rate Setting: This determines the typematic rate.

**Enabled**: Enable typematic rate and typematic delay programming.

**Disabled**: Disable typematic rate and typematic delay programming. The system BIOS will use default value of 2 items and the default is controlled by the keyboard.

• Typematic Rate(Chars/Sec):

6:6 characters per second.

10: 10 characters per second.

15: 15 characters per second.

24: 24 characters per second.

26: 8 characters per second.

26: 12 characters per second.

20: 20 characters per second.

20: 30 characters per second.

• **Typematic Delay(Msec):** This detecmines the time between the first and second character displayed, when holding a key.

250:250msec.

500:500 msec.

750:750 msec.

1000:1000msec.

Security Option: This category allows you to limit access to the system and Setup, or just to Setup. The default value is Setup.

**System**: The system will not boot and the access to Setup will be denied if the correct password is not entered at the prompt.

**Setup**: The system will boot, but the access to Setup will be denied if the correct password is not entered at the prompt.

PCI/VGA Palette Snoop: This filed controls the ability of a primary PCI VGA

controller to share a common palette (when a snoop write cycles) with an ISA

video card. The default value is Disabled.

**Enabled:** If an ISA card connects to a PCI VGA card via the VESA connector and the ISA card connects to VGA monitor and uses the RAMDAC of PCI card, the PCI/VGA Palette Snoop is enabled.

**Disabled:** Disable the VGA card Palette snoop function.

Video BIOS Shadow: It determines whether video BIOS will be copied to RAM, however, it is optional from chipset design. Video Shadow will increase the video speed.

Enabled: Video shadow is enabled.Disabled: Video shadow is disabled.

C8000 - CBFFF Shadow:

CC000 - CFFFF Shadow:

D0000 - D3FFF Shadow:

D4000 - D7FFF Shadow:

D8000 - DBFFF Shadow:

DC000 - DFFFF Shadow:

These categories determine whether optional ROM will be copied to RAM by 16K byte or 32K byte perunit and the size depends on the chipset.

Enabled: Optional shadow is enabled.Disabled: Optional shadow is disabled.

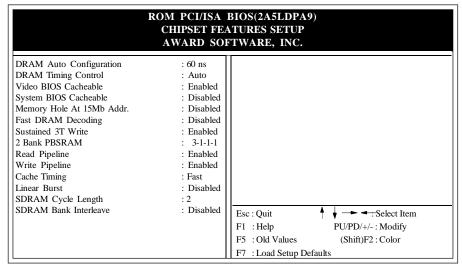

#### 3-3 CHIPSET FEATURES SETUP

Choose the "CHIPSET FEATURES SETUP" in the CMOS SETUP UTILITY menu to display the following menu.

Figure 3-4 CHIPSET FEATURES SETUP

**Note:** When you insert slower memery modules in the system and set a faster timing, maybe the system will hang up.

• **DRAM Timing:** The default value is 60ns.

60ns: 2 (faster) Burst Wait State, for 60~70ns Fast Page Mode/EDO DRAM. 70ns: 3 (slower) Burst Wait State, for 70ns Fast Page Mode/EDO DRAM.

• Video BIOS Cacheable: The default value is Enabled.

*Enabled*: Enabled the Video BIOS Cacheable to speed up the VGA Performance.

Disabled: Disabled the Video BIOS Cacheable function.

• Memory Hole at 15M-16M: The default value is Disabled.

Disabled: Normal Setting.

**Enabled:** This field enableds the main memory (15~16MB) remap to ISA BUS.

#### 3-4 POWER MANAGEMENT SETUP

Choose the "POWER MANAGEMENT SETUP" in the CMOS SETUP UTILITY to display the following screen. This menu allows the user to modify the power management parameters and IRQ signals. In general, these parameters should not be changed unless it is absolutely necessary.

|                                                                                                                                                                                     | POWER MANAG<br>AWARD SOFT                                                                                    |                                                                                                                                                                                                                                                        |                                                                                                                                     |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| Power Management PM Control by APM Video off Option Video off Method Conserve Mode Modem Use IRO **PM Timers ** HDD Power Down Doze Mode Suspend Mode  **PM Events ** VGA LPT & COM | : User Define : Yes : Suspend -> Off : V/H SYNC+Blank : Disabled : 3 : Disable : Disable : Disable : Disable | ** Power Down & Resume Ev<br>IRQ5 (LPT 2)<br>IRQ6 (Floppy Disk)<br>IRQ7 (LPT 1)<br>IRQ8 (RTC Alarm)<br>IRQ9 (IRQ2 Redir)<br>IRQ10 (Reserved)<br>IRQ11 (Reserved)<br>IRQ12 (PS/2 Mouse)<br>IRQ13 (Coprocessor)<br>IRQ14 (Hard Disk)<br>IRQ15 (Reserved) | : Primary : Disabled : Primary : Disabled : Primary |

| HDD & FDD<br>DMA /master<br>Primary INTR<br>IRQ3 (COM 2)<br>IRQ4 (COM 1)                                                                                                            | : OFF<br>: OFF<br>: ON<br>: Primary<br>: Primary                                                             | F1 : Help PU/                                                                                                                                                                                                                                          | → ÷ Select Item PD/+/- : Modify hift)F2 : Color                                                                                     |

Figure 3-5 POWER MANAGEMENT SETUP

Again, user can move the cursor by pressing direction keys to the field needed to be modified and press <PgDn> or <PgUp> to alter item selection. You can only change the content of **Doze Mode**, **Standby Mode**, and **Suspend Mode** when the **Power Management** is set to '**User Define**'.

# 3-4-1 The Description of the Power Management

## A. Power Management mode selection:

**Disabled**: The system operates in NORMAL conditions (Non-GREEN) and the Power Management function is disabled.

Max. saving: This mode will maximize the power saving capability.

**Min. saving:** This mode will minimize the power saving capability.

**User define:** Allow user to define time-out parameters to control power saving mode. Refer to item B shown below.

#### **B.** Time-out parameters:

#### **HDDStandby**

HDD Standby timer can be set from 1 to 15 minute(s).

#### System Doze

The "System Doze" mode timer starts to count when there is no "PM events" occurred. The valid time-out setting is from 1 minute up to 1 hour.

#### **System Suspend**

This function works only when the Pentium Procssor is installed. The timer starts to count when "System Standby" mode timer is timed out and no "PM Events" occurred. Valid range is from 1 minute up to 1 hour.

#### 3-4-2 Description of the Green Functions

The 5BVPXA supports HDD Power Down, Doze and Suspend power saving functions. In addition, the hardware suspend function is supported when the J5-SLEEP (Refer to Figure 1-1) is closed to enter the Suspend function.

The detailed description of these functions is provided in the next page.

#### **HDDStandby Mode**

When system stops reading or wiriting HDD, the timer starts to count. The system will cut off the HDD power when timer runs out of time. The system will not resume operation until either a read from or a wirte to HDD command is executed again.

#### DozeMode

The system hardware will drop down CPU clock from nomal working speed when Doze mode time-out occurs.

#### Suspend Mode

When the system suspend timer times out, the system will enter the suspend mode and the chipset will stop CPU clock immediately. The power consumption in Suspend Mode is lower than in standby mode. The screen is also blanked out.

#### **PM Events:**

AWARD BIOS defines 15 PM Events in the power management mode (Doze & suspend). The user can initialize any PM Events to be "Enable" or "Disable". When the system detects all of the enabled events, do not have any activity. It will start the system Doze timer first if the "Power Management" is not "Disabled". Once the system Doze timer is timed out, it will process doze power saving procedure by starting the system suspend timer. When the suspend timer times out, all of the CPU clock will stop by dropping system clock down to zero and remains this way until any one of the "Enabled" event occurrs.

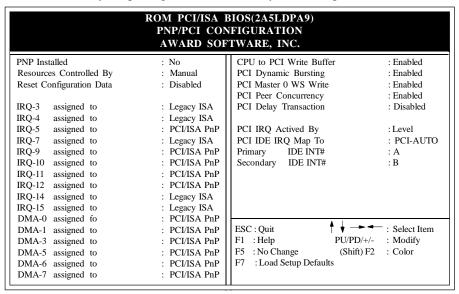

#### 3-5 PNP/PCI CONFIGURATION

The PNP/PCI configuration program is for the user to modify the PCI/ISA IRQ signals when various PCI/ISA cards are inserted in the PCI or ISA slots.

**WARNING**: Any misplacing IRQ could cause system can't pick out the rescouces.

Figure 3-6 PCI CONFIGURATION SETUP

• Resource Controlled By: The default value is Manual.

**Manual:** The field defines that the PNP Card's resource is controlled by manual.

You can set whethe IRQ-X or DMA-X is assigned to PCI/ISA PNP or

Legacy ISA Cards.

**Auto:** If your ISA card and PCI card are all PNP cards. Set this field Auto.

The BIOS will assign the interrupt resource automatically.

• Reset Configuration Data: The default value is Disabled.

**Disabled:** Normal Setting

**Enabled:** If you plug some Legacuy cards in the system and record into ESCD (Extended System Configuration Data). You can set this field to be Enabled and to clear ESCD at one time, when some Legacy cards are removed.

#### • **PCIIDE IRQ Map To:** The default value is PCI-AUTO.

When you have true PCI card(s) plugged into the system, you will not need to change any thing here in the **SETUP** program. However, if you do not know whether you are using a true PCI card, please refer to your PCI card user's manual for the details.

When you have a Legacy card (described in section 2-5) to plug into the system, a proper setting is extremely important or it may cause the system hung up. The diagram shown below tells you how the Rotating Priority Mechanism is designed.

Figure 3-7 The Combination of PCI INT# lines

#### 3-6 INTEGRATED PERIPHERALS

| ROM PCI/ISA BIOS(2A5LDPA9)<br>INTEGRATED PERIPHERALS<br>WARD SOFTWARE, INC. |            |                          |             |  |

|-----------------------------------------------------------------------------|------------|--------------------------|-------------|--|

| Onboard Primary PCI IDE                                                     |            | Onboard Parallel Port    | : 378/IRQ7  |  |

| Onboard Secondary PCI IDE                                                   |            | Onboard Parallel Mode    | : ECP / EPP |  |

| IDE Prefetch Mode                                                           |            | ECP Mode Use DMA         |             |  |

|                                                                             | : Enabled  | Parallel Port EPP Type   | : EPP1.9    |  |

| IDE primary Master PIO                                                      |            |                          |             |  |

|                                                                             | : Auto     | Onboard USB Controller   | : Disabled  |  |

| IDE Secondary Master PIO                                                    | : Auto     |                          |             |  |

| IDE Secondary Slave PIO                                                     | : Auto     |                          |             |  |

| IDE Primary Master UDMA                                                     | : Auto     |                          |             |  |

| IDE Primary Slave UDMA                                                      | : Auto     |                          |             |  |

| IDE Secondary Master UDMA                                                   | : Auto     |                          |             |  |

| IDE Secondary Slave UDMA                                                    | : Auto     |                          |             |  |

| PCI IDE Secondary Channel                                                   | : Enabled  |                          |             |  |

|                                                                             | : Enabled  |                          |             |  |

| UART 2 Mode                                                                 | : Standard | ESC : Quit               | Select Item |  |

|                                                                             |            | F1 : Help PU/PD/+        | /- : Modify |  |

|                                                                             |            | F5 : No Change (Shift) F | 2 : Color   |  |

|                                                                             |            | F7 : Load Setup Defaults |             |  |

Note: If you don't use the Onboard IDE connector, then use On-card (PCI or ISA card) IDE connector. You have to set Onboard Primary PCI IDE: Disabled and Onboard Secondary PCI IDE: Disabled from CHIPSET FEATURES SETUP UTILITY.

The Onboard PCI IDE cable should be equal to or less than 18 inches (45 cm.).

• **IDE HDD Block Mode:** The default value is Enabled.

**Enabled**: Enabled IDE HDD Block Mode. The HDD transfer rate is better than Disable.

**Disabled**: Disable IDE HDD Block Mode.

• PCI Slot IDE 2nd Channel: The default value is Enabled.

Enabled: Enable secondary IDE port and BIOS will assign IRQ15 for this port.Disabled: Disable secondary IDE port and IRQ15 is available for other device.

• Onboard Primary PCI IDE: The default value is Enabled.

**Enabled**: Enable Onboard 1st channel IDE port.

**Disabled**: Disable Onboard 1st channel IDE port. When use On-card (PCI or ISA card) IDE connector.

• Onboard Secondary PCI IDE: The default value is Enabled.

*Enabled*: Enable Onboard 2nd channel IDE port.

**Disabled**: Disable Onboard 2nd channel IDE port When use On-card (PCI or ISA card) IDE connector.

• IDE Primary Master PIO: The default value is Auto.

Auto : BIOS will automatically detect the Onboard Primary Master PCI

IDE HDD Accessing mode.

*Mode0-4* : Manually set the IDE Accessing mode.

• **IDE Primary Slave PIO:** The default value is Auto.

Auto: BIOS will automatically detect the Onboard Primary Slave PCI IDE

HDD Accessing mode.

*Mode0-4* : Manually set the IDE Accessing mode.

• **IDE Secondary Master PIO:** The default value is Auto.

Auto: BIOS will automatically detect the Onboard Secondary Master PCI

IDE HDD Accessing mode.

*Mode0-4* : Manually set the IDE Accessing mode.

• **IDE Secondary Slave PIO:** The default value is Auto.

Auto : BIOS will automatically detect the Onboard Secondary Slave PCI

IDE HDD Accessing mode.

*Mode0-4* : Manually set the IDE Accessing mode.

• Onboard FDC Controller: The default value is Enabled.

Enabled : Enable the Onboard SMC CHIP's floppy drive interface controller.

Disable the Onboard SMC CHIP's floppy drive interface controller,

When using On-card ISA FDC's controller.

• **Onboard UART 1:** This field allows the user to sellect the serial port. The default value is 3F8H/IRQ4.

**COMI**: Enable Onboard Serial port 1 and address is 3F8H/IRQ4.

**COM2**: Enable Onboard Serial port 1 and address is 2F8H/IRQ3.

COMB: Enable Onboard Serial port 1 and address is 3E8H/IRQ4.

COM4: Enable Onboard Serial port 1 and address is 2E8H/IRQ3.

Disabled: Disable Onboard SMC CHIP's Serial port 1.

Onboard UART 2: This field allows the user to sellect the serial port. The default value is 2F8H/IRQ3.

**COMI**: Enable Onboard Serial port 2 and address is 3F8H/IRQ4.

**COM2**: Enable Onboard Serial port 2 and address is 2F8H/IRQ3.

**COM3**: Enable Onboard Serial port 2 and address is 3E8H/IRQ4.

COM4: Enable Onboard Serial port 2 and address is 2E8H/IRQ3.

Disabled: Disable Onboard SMC CHIP's Serial port 2.

• Onboard UART 2 Mode: The default value is standard. This field allows the User to select the COM2 port that can support a serial Infrared Interface.

**Standard:** Support a Serial Infrared Interface IrDA. **HPSIR:** Support a HP Serial Infrared Interface format. **ASKIR:** Support a Sharp Serial Infrared Interface format.

• **Onboard Parallel port:** This field allows the user to sellect the LPT port. The default value is 378H/IRQ7.

378H : Enable Onboard LPT port and address is 378H and IRQ7

278H : Enable Onboard LPT port and address is 278H and IRQ5.

3BCH : Enable Onboard LPT port and address is 3BCH and IRQ7.

**Disabled**: Disable Onboard SMC CHIP's LPT port.

NOTE: Parallel Port address is 378H/3BCH that selects the rounting of IRQ7 for LPT1.

Parallel Port address is 278H that selects the rounting of IRQ5 for LPT1.

• Parallel port Mode: This field allows the user to sellect the parallel port mode.

The default value is ECP+EPP.

Normal: Standard mode. IBM PC/AT Compatible bidirectional parallel port.

EPPEnhanced Parallel Port mode.ECPExtended Capability Port mode.EPP+ECPECP Mode & EPP Mode.

**ECP Mode USE DMA:** This field allows the user to sellect DMA1 or DMA3 for the ECP mode. The default value is DMA3.

DMA1 : The filed selects the rounting of DMA1 for the ECP mode.

DMA3 : The filed selects the rounting of DMA3 for the ECP mode.

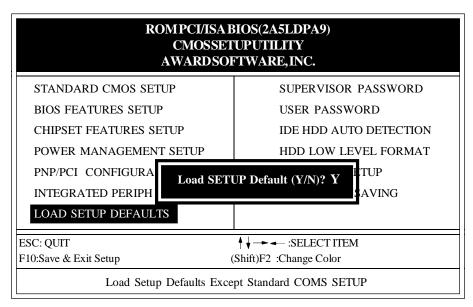

#### 3-7 LOAD SETUP DEFAULTS

The "LOAD SETUP DEFAULTS" function loads the system default data directly from ROM and initializes the associated hardware properly. This function will be necessary only when the system CMOS data is corrupted.

Figure 3-8 LOAD SETUP DEFAULT

#### 3-8 CHANGE SUPERVISOR or USER PASSWORD

To change the password, choose the "SUPERVISOR PASSWORD or USER PASSWORD" option from the CMOS SETUP UTILITY menu and press [Enter].

**NOTE**: Either "Setup" or "System" must be selected in the "Security Option" of the BIOS FEATURES SETUP menu (Refer to Figure 3-3 for the details).

1. If CMOS is corrupted or the option is not used, a default password stored in the ROM will be used. The screen will display the following message:

#### Enter Password:

Press the [Enter] key to continue after proper password is given.

If CMOS is corrupted or the option was used earlier and the user wish to change default password, the SETUP UTILITY will display a message and ask for a confirmation.

#### Confirm Password:

3. After pressing the [Enter] key (ROM password if the option was not used) or current password (user-defined password), the user can change the password and store new one in CMOS RAM. A maximum of 8 characters can be entered.

#### 3-9 IDE HDD AUTO DETECTION

The "IDE HDD AUTO DETECTION" utility is a very useful tool especially when you do not know which kind of hard disk type you are using. You can use this utility to detect the correct disk type installed in the system automatically. **But now** you can set **HARD DISK TYPE** to **Auto** in the **STANDARD CMOS SETUP**. You do not need the "IDE HDD AUTO DETECTION" utility. The BIOS will Auto-detect the hard disk size and model on display during POST.

Figure 3-9 IDE HDD AUTO DETECTION

#### **NOTE: HDD Modes**

The Award BIOS supports 3 HDD modes : NORMAL, LBA and LARGE NORMAL mode.

Generic access mode that is neither the BIOS nor the IDE controller will make transformations during accessing.

The maximum nunbers of cylinders, head & sectors for NORMAL mode are 1024, 16 and 63.

| ne            | o. Cyclinder  | (1024) |  |

|---------------|---------------|--------|--|

| x n           | o. Head       | (16)   |  |

| x n           | o. Sector     | (63)   |  |

| x n           | o. per sector | (512)  |  |

| 528 Megabytes |               |        |  |

If user sets his HDD to NORMAL mode, the maximum accessible HDD size will be 528 Megabytes even though its physical size may be greater than that!

**LBA** (**Logical Block Addressing**) **mode:** This is a new HDD accessing method to overcome the 528 Megabyte bottleneck.

The number of cylinders, heads and sectors shown in the setup may not be the number physically contained in the HDD.

During the HDD accessing, the IDE controller will transform the logical address described by sector, head and cylinder into its own physical address inside the HDD.

The maximum HDD size supported by LBA mode is 8.4 Gigabytes which is obtained by the following formula:

| no. Cyclinder       | (1024) |

|---------------------|--------|

| x no. Head          | (255)  |

| x no. Sector        | ( 63)  |

| x bytes per secttor | (512)  |

| 8.4 Gigabytes       |        |

**LARGE mode:** This is an extended HDD access mode supported by Award Software.

Some IDE HDDs contain more than 1024 cylinders without LBA support (in some cases, user does not want LBA). The Award BIOS provides another alternative to support these kinds of LARGE mode:

| CYLS. | HEADS | SECTOR | MODE   |

|-------|-------|--------|--------|

| 1120  | 16    | 59     | NORMAL |

| 560   | 32    | 59     | LARGE  |

BIOS tricks DOS (or other OS) that the number of cylinders is less than 1024 by dividing it by 2. At the same time, the number of heads is multiplied by 2. A reverse transformation process will be made inside INT 12h in order to access the right HDD address

Maximum HDD size:

| no. Cyclinder      | (1024) |

|--------------------|--------|

| x no. Head         | ( 32)  |

| x no. Sector       | (63)   |

| x bytes per sector | (512)  |

| 1 Gigabytes        |        |

#### Note:

To support LBA or LARGE mode of HDDs, there must be some softwares involved. All softwares are located in the Award HDD Service Routine (1NT 13h). It may fail to access a HDD with LBA (LARGE) mode selected if you are running under on Operating System which replaces the whole 1NT 13h. UNIX operating systems do not support either LBA or LARGE and must utilize the Standard mode. UNIX can support drives larger than 528MB.

#### 3-10 HDD LOW LEVEL FORMAT

#### **Interleave**

Select the interleavenumber of the harddisk drive that you wish to perform a low level format on. You may select from 1 to 8. Check the documentation that came with the drive for the correct interleavenumber, or select 0 for automatic detection.

#### Auto scan bad track

This allows the utility to scan first then format by each track.

#### Start

Press<Y>to start low level format.

#### 3-11 SAVE & EXIT SETUP

The "SAVE & EXIT SETUP" option will bring you back to boot up procedure with all the changes you just recorded in the CMOS RAM.

## 3-12 EXIT WITHOUT SAVING

The "EXIT WITHOUT SAVING" option will bring you back to normal boot up procedure without saving any data into CMOS RAM. All old data in the CMOS will not be destroyed.

# Chapter 4

# **Technical Information**

# 4-1 I/O & MEMORY MAP

#### **MEMORY MAP**

[3F8-3FF]

| Address Range | Size | Description                                        |

|---------------|------|----------------------------------------------------|

| [00000-7FFFF] | 512K | Conventional memory                                |

| [80000-9FBFF] | 127K | Extended Conventional memory                       |

| [9FC00-9FFFF] | 1K   | Extended BIOS data area if PS/2 mouse is installed |

| [A0000-C7FFF] | 160K | Available for Hi DOS memory                        |

| [C8000-DFFFF] | 96K  | Available for Hi DOS memory and adapter ROMs       |

| [E0000-EEFFF] | 60K  | Available for UMB                                  |

| [EF000-EFFFF] | 4K   | Video service routine for Monochrome & CGA adaptor |

| [F0000-F7FFF] | 32K  | BIOS CMOS setup utility                            |

| [F8000-FCFFF] | 20K  | BIOS runtime service routine (2)                   |

| [FD000-FDFFF] | 4K   | Plug and Play ESCD data area                       |

| [FE000-FFFFF] | 8K   | BIOS runtime service routine (1)                   |

| I/O MAP       |      |                                                    |

| 5000 04EI     |      | DMA ( II (M. )                                     |

| [000-01F]     |      | DMA controller.(Master)                            |

| [020-021]     |      | INTERRUPT CONTROLLER.(Master)                      |

| [022-023]     |      | CHIPSET control registers. I/O ports.              |

| [040-05F]     |      | TIMER control registers.                           |

| [060-06F]     |      | KEYBOARD interface controller.(8042)               |

| [070-07F]     |      | RTC ports & CMOS I/O ports.                        |

| [080-09F]     |      | DMA register.                                      |

| [0A0-0BF]     |      | INTERRUPT controller.(Slave)                       |

| [0C0-0DF]     |      | DMA controller.(Slave)                             |

| [0F0-0FF]     |      | MATH COPROCESSOR.                                  |

| [1F0-1F8]     |      | HARD DISK controller.                              |

| [278-27F]     |      | PARALLEL port 2.                                   |

| [2B0-2DF]     |      | GRAPHICS adapter controller.                       |

| [2F8-2FF]     |      | SERIAL port 2.                                     |

| [360-36F]     |      | NETWORK ports.                                     |

| [378-37F]     |      | PARALLEL port 1.                                   |

| [3B0-3BF]     |      | MONOCHROME & PARALLEL port adapter.                |

| [3C0-3CF]     |      | EGA adapter.                                       |

| [3D0-3DF]     |      | CGA adapter.                                       |

| [3F0-3F7]     |      | FLOPPY DISK controller.                            |

SERIAL port 1.

#### 4-2 TIME & DMA CHANNELS MAP

**TIME MAP:** TIMER Channel 0 System timer interrupt.

TIMER Channel 1 DRAM REFRESH request.

TIMER Channel 2 SPEAKER tone generator.

**DMA CHANNELS:** DMA Channel 0 Available.

DMA Channel 1 Onboard ECP (Option).

DMA Channel 2 FLOPPY DISK (SMC CHIP).

DMA Channel 3 Onboard ECP (default).

DMA Channel 4 Cascade for DMA controller 1.

DMA Channel 5 Available.

DMA Channel 6 Available.

DMA Channel 7 Available.

#### **4-3 INTERRUPT MAP**

**NMI:** Parity check error.

**IRQ** (H/W): 0 System TIMER interrupt from TIMER 0.

1 KEYBOARD output buffer full.

2 Cascade for IRQ 8-15.

3 SERIAL port 2.

4 SERIAL port 1.

5 PARALLEL port 2.

6 FLOPPY DISK (SMC CHIP).

7 PARALLEL port 1.

8 RTC clock.

9 Available.

10 Available.

11 Available.

12 PS/2 Mouse.

13 MATH coprocessor.

14 Onboard HARD DISK(IDE1) channel.

15 Onboard HARD DISK(IDE2) channel.

# 4-4 RTC & CMOS RAM MAP

| RTC & CMOS: | 00    | Seconds.                                 |

|-------------|-------|------------------------------------------|

| RIC & CMOS. | 01    | Second alarm.                            |

|             | 02    | Minutes.                                 |

|             | 03    | Minutes alarm.                           |

|             | 03    | Hours.                                   |

|             | 05    | Hours alarm.                             |

|             | 06    | Day of week.                             |

|             | 07    | Day of month.                            |

|             | 08    | Month.                                   |

|             | 09    | Year.                                    |

|             | 0A    | Status register A.                       |

|             | 0B    | Status register B.                       |

|             | 0C    | Status register C.                       |

|             | 0D    | Status register D.                       |

|             | 0E    | Diagnostic status byte.                  |

|             | 0F    | Shutdown byte.                           |

|             | 10    | FLOPPY DISK drive type byte.             |

|             | 11    | Reserve.                                 |

|             | 12    | HARD DISK type byte.                     |

|             | 13    | Reserve.                                 |

|             | 14    | Equipment type.                          |

|             | 15    | Base memory low byte.                    |

|             | 16    | Base memory high byte.                   |

|             | 17    | Extension memory low byte.               |

|             | 18    | Extension memory high byte.              |

|             | 19-2d |                                          |

|             | 2E-2F |                                          |

|             | 30    | Reserved for ectension memory low bytw.  |

|             | 31    | Reserved for extension memory high byte. |

|             | 32    | DATE CENTURY byte.                       |

|             | 33    | INFORMATION FLAG.                        |

|             | 34-3F | Reserve.                                 |

|             | 40-7F | Reserved for CHIPSET SETTING DATA.       |

#### APPENDIX A: POST CODES

ISA POST codes are typically output to port address 80h.

#### POST(hex) DESCRIPTION 01-02 Reserved. C0Turn off OEM specific cache, shadow. 03 1.Initialize EISA registers (EISA BIOS only). 2.Initialize all the standard devices with default values Standard devices includes. -DMA controller (8237). -Programmable Interrupt Controller (8259). -Programmable Interval Timer (8254). -RTC chip. 04 Reserved 05 1.Keyboard Controller Self-Test. 2. Enable Keyboard Interface. 06 Reserved. **07** Verifies CMOS's basic R/W functionality. **C1** Auto-detection of onboard DRAM & Cache. **C5** Copy the BIOS from ROM into E0000-FFFFF shadow RAM so that POST will go faster. 08 Test the first 256K DRAM. 09 OEM specific cache initialization. (if needed) 0A1.Initialize the first 32 interrupt vectors with corresponding Interrupt handlers Initialize INT no from 33-120 with Dummy (Suprious) Interrupt Handler. 2.Issue CPUID instruction to identify CPU type. 3.Early Power Management initialization. (OEM specific) 0B1. Verify the RTC time is valid or not. 2.Detect bad battery. 3.Read CMOS data into BIOS stack area. 4.PnP initializations including. (PnP BIOS only) -Assign CSN to PnP ISA card. -Create resource map from ESCD.

5. Assign IO & Memory for PCI devices. (PCI BIOS only)

| POST(hex) | DESCRIPTION                                                                                                                                                                                                                                                                                              |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0C        | Initialization of the BIOS Data Area. (40:ON - 40:FF)                                                                                                                                                                                                                                                    |

| 0D        | <ol> <li>Program some of the Chipset's value according to Setup. (Early Setup Value Program)</li> <li>Measure CPU speed for display &amp; decide the system clock speed.</li> <li>Video initialization including Monochrome, CGA, EGA/VGA. If no display device found, the speaker will beep.</li> </ol> |

| 0E        | 1.Test video RAM. (If Monochromc display device found) 2.Show messages including.  -Award Logo, Copyright string, BIOS Data code & Part No.  -OEM specific sign on messages.  -Energy Star Logo. (Green BIOS ONLY)  -CPU brand, type & speed.  -Test system BIOS checksum. (Non-Compress Version only)   |

| <b>0F</b> | DMA channel 0 test.                                                                                                                                                                                                                                                                                      |

| 10        | DMA channel 1 test.                                                                                                                                                                                                                                                                                      |

| 11        | DMA page registers test.                                                                                                                                                                                                                                                                                 |

| 12-13     | Reserved.                                                                                                                                                                                                                                                                                                |

| 14        | Test 8254 Timer 0 Counter 2.                                                                                                                                                                                                                                                                             |

| 15        | Test 8259 interrupt mask bits for channel 1.                                                                                                                                                                                                                                                             |

| 16        | Test 8259 interrupt mask bits for channel 2.                                                                                                                                                                                                                                                             |

| 17        | Reserved.                                                                                                                                                                                                                                                                                                |

| 19        | Test 8259 functionality.                                                                                                                                                                                                                                                                                 |

| 1A-1D     | Reserved.                                                                                                                                                                                                                                                                                                |

| 1E        | If EISA NVM checksum is good, execute EISA initialization. (EISA BIOS only)                                                                                                                                                                                                                              |

| 1F-29     | Reserved.                                                                                                                                                                                                                                                                                                |

| 30        | Detect Base Memory & Extended Memory Size.                                                                                                                                                                                                                                                               |

| 31        | <ul><li>1.Test Base Memory from 256K to 640K.</li><li>2.Test Extended Memory from 1M to the top of memory.</li></ul>                                                                                                                                                                                     |

# 4-6 CHAPTER 4

| POST(hex) | DESCRIPTION                                                                                                                                                                                             |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 32        | 1.Display the Award Plug & Play BIOS Extension message. (PnP BIOS only) 2.Program all onboard super I/O chips (if any) including COM ports, LPT ports, FDD port according to setup value.               |

| 33-3B     | Reserved.                                                                                                                                                                                               |

| 3C        | Set flag to allow users to enter CMOS Setup Utility.                                                                                                                                                    |

| 3D        | 1.Initialize Keyboard. 2.Install PS2 mouse.                                                                                                                                                             |

| 3E        | Try to turn on Level 2 cache.  Note: Some chipset may need to turn on the L2 cache in this stage. But usually, the cache is turn on later in POST 61h.                                                  |

| 3F-40     | Reserved.                                                                                                                                                                                               |

| BF        | <ul><li>1.Program the rest of the Chipset's value according to Setup. (Later Setup Value Program)</li><li>2.If auto-configuration is enabled, programmed the chipset with pre-defined Values.</li></ul> |

| 41        | Initialize floppy disk drive controller.                                                                                                                                                                |

| 42        | Initialize Hard drive controller.                                                                                                                                                                       |

| 43        | If it is a PnP BIOS, initialize serial & parallel ports.                                                                                                                                                |

| 44        | Reserved.                                                                                                                                                                                               |

| 45        | Initialize math coprocessor.                                                                                                                                                                            |

| 46-4D     | Reserved.                                                                                                                                                                                               |

| 4E        | If there is any error detected (such as video, kb), show all the error messages on the screen & wait for user to press <f1> key.</f1>                                                                   |

| <b>4F</b> | <ul><li>1.If password is needed, ask for password.</li><li>2.Clear the Energy Star Logo. (Green BIOS only)</li></ul>                                                                                    |

| 50        | Write all CMOS values currently in the BIOS stack area back into the CMOS.                                                                                                                              |

| 51        | Reserved.                                                                                                                                                                                               |

#### POST(hex) DESCRIPTION

52 1.Initialize all ISA ROMs.

2.Later PCI initializations. (PCI BIOS only)

-assign IRQ to PCI devices.

-initialize all PCI ROMs.

3.PnP Initialzations. (PnP BIOS only)

-assign IO, Memory, IRQ & DMA to PnP ISA devices.

-initialize all PnP ISA ROMs.

4.Program shadows RAM according to Setup settings.

5.Program parity according to Setup setting.

6.Power Management Initialization.

-Enable/Disable global PM.

-APM interface initialization.

53 1.If it is NOT a PnP BIOS, initialize serial & paralled ports.

2.Initialize time value in BIOS data area by translate the RTC time value into a timer tick value.

60 Setup Virus Protection. (Boot Sector Protection) functionality according to Setup setting.

61 1.Try to turn on Level 2 cache.

Note: if L2 cache is already turned on in POST 3D, this part will be skipped.

2.Set the boot up speed according to Setup setting.

3.Last chance for Chipset initialization.

4.Last chance for Power Management initialization. (Green BIOS only)

5.Show the system configuration table.

62 1.Setup daylight saving according to Setup value.

Program the NUM Lock, typematic rate & typematic speed according to Setup setting.

1.If there is any changes in the hardware configuration, update the ESCD information. (PnP BIOS only)

2.Clear memory that have been used.

3.Boot system via INT 19H.

**FF** System Booting. This means that the BIOS already pass the control right to the operating system.

#### **Unexpected Errors:**

#### POST(hex) DESCRIPTION

**B0** If interrupt occurs in protected mode.

**B1** Unclaimed NMI occurs.

### APPENDIX B: I/O CONNECTORS

## **CN6: USB CONNECTOR:**

| Signal Name                                              | Pin                   | Pin                       | Signal Name                                    |

|----------------------------------------------------------|-----------------------|---------------------------|------------------------------------------------|

| USB_VCC<br>USB_data0-<br>USB_data0+<br>Ground<br>USB_VCC | 1<br>2<br>3<br>4<br>5 | 9<br>10<br>11<br>12<br>13 | Ground<br>Ground<br>Ground<br>Ground<br>Ground |

| USB_data1-                                               | 6                     | 14                        | Ground                                         |

| USB_data1+                                               | 7                     | 25                        | Ground                                         |

| Ground                                                   | 8                     | 26                        | Ground                                         |

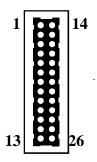

# CN1/COM1,CN2/COM2: Serial Ports Connector

| Signal Name                      | Pin                   | Pin                    | Signal Name                     |

|----------------------------------|-----------------------|------------------------|---------------------------------|

| DCD<br>SIN<br>SOUT<br>DTR<br>GND | 1<br>2<br>3<br>4<br>5 | 6<br>7<br>8<br>9<br>10 | DSR<br>RTS<br>CTS<br>RI<br>N.C. |

|                                  |                       |                        |                                 |

# **CN7: Parallel Port Connector**

| Signal Name | Pin | Pin | Signal Name |

|-------------|-----|-----|-------------|

| STROBE-     | 1   | 14  | AUTO FEED-  |

| Data Bit 0  | 2   | 15  | ERROR-      |

| Data Bit 1  | 3   | 16  | INIT-       |

| Data Bit 2  | 4   | 17  | SLCT IN-    |

| Data Bit 3  | 5   | 18  | Ground      |

| Data Bit 4  | 6   | 19  | Ground      |

| Data Bit 5  | 7   | 20  | Ground      |

| Data Bit 6  | 8   | 21  | Ground      |

| Data Bit 7  | 9   | 22  | Ground      |

| ACJ-        | 10  | 23  | Ground      |

| BUSY        | 11  | 24  | Ground      |

| PE          | 12  | 25  | Ground      |

| SLCT        | 13  | 26  | N.C.        |

|             |     |     |             |

CN3: Floppy Disk Connector

| Signal Name | Pin | Pin | Signal Name     |

|-------------|-----|-----|-----------------|

| Ground      | 1   | 2   | FDHDIN          |

| Ground      | 3   | 4   | Reserved        |

| Ground      | 5   | 6   | FDEDIN          |

| Ground      | 7   | 8   | Index-          |

| Ground      | 9   | 10  | Motor Enable    |

| Ground      | 11  | 12  | Drive Select B- |

| Ground      | 13  | 14  | Drive Select A- |

| Ground      | 15  | 16  | Motor Enable    |

| Ground      | 17  | 18  | DIR-            |

| Ground      | 19  | 20  | STEP-           |

| Ground      | 21  | 22  | Write Data      |

| Ground      | 23  | 24  | Write Gate      |

| Ground      | 25  | 26  | Track 00-       |

| Ground      | 27  | 28  | Write Protect-  |

| Ground      | 29  | 30  | Read Data-      |

| Ground      | 31  | 32  | SIDE 1 SELECT-  |

| Ground      | 33  | 34  | Diskette        |

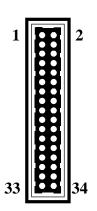

CN4/CN5: Primary, Secondray IDE Connector

| Signal Name    | Pin | Pin | Signal Name    |

|----------------|-----|-----|----------------|

| Reset IDE      | 1   | 2   | Ground         |

| Host Data 7    | 3   | 4   | Host Data 8    |

| Host Data 6    | 5   | 6   | Host Data 9    |

| Host Data 5    | 7   | 8   | Host Data 10   |

| Host Data 4    | 9   | 10  | Host Data 11   |

| Host Data 3    | 11  | 12  | Host Data 12   |

| Host Data 2    | 13  | 14  | Host Data 13   |

| Host Data 1    | 15  | 16  | Host Data 14   |

| Host Data 0    | 17  | 18  | Host Data 15   |

| Ground         | 19  | 20  | Key            |

| DRQ3           | 21  | 22  | Ground         |

| I/O Write-     | 23  | 24  | Ground         |

| I/O Read-      | 25  | 26  | Ground         |

| IOCHRDY        | 27  | 28  | BALE           |

| DACK3-         | 29  | 30  | Ground         |

| IRQ14          | 31  | 32  | IOCS16-        |

| Addr 1         | 33  | 34  | Ground         |

| Addr 0         | 35  | 32  | Addr 2         |

| Chip Select 0- | 37  | 38  | Chip Select 1- |

| Activity       | 39  | 40  | Ground         |